# Formal Semantics Extraction from Natural Language Specifications for ARM

# Viet Anh Vu

Graduate School of Advanced Science and Technology Japan Advanced Institute of Science and Technology December, 2018

## Master's Thesis

# Formal Semantics Extraction from Natural Language Specifications for ARM

# 1610432 Viet Anh Vu

Supervisor : Mizuhito Ogawa Main Examiner : Mizuhito Ogawa Examiners : Kazuhiro Ogata Nguyen Minh Le Keita Yokoyama

Graduate School of Advanced Science and Technology Japan Advanced Institute of Science and Technology [Information Science] November, 2018

# Abstract

Recently, Malware Analysis has been received much attention not only in industry but also in the academic community. Modern malware frequently applies obfuscation techniques (e.g., indirect jump, overlapping instruction) to conceal its behaviors and protect itself against antivirus software, which regularly uses lightweight detection methods like bitbased fingerprints. Since famous commercial disassemblers such as IDA Pro and Capstone are easily fooled by these obfuscations, analyzing and detecting the obfuscated malware are not straightforward. For dealing with these problems, some malware analysis approaches based on Control Flow Graph (CFG) have been proposed (e.g., VxClass at Google). To effectively reconstruct the CFG, a technique called Dynamic Symbolic Execution (DSE) (known as concolic testing) has been widely applied. It is the combination of symbolic execution and testing to automatically explore all feasible program execution paths and determine the destination of obfuscation code like indirect jumps (by using a binary emulator). In DSE, the feasibility of a path constraint is checked by testing with a satisfiable instance using a Theorem Prover. Currently, we have developed BE-PUM (Binary Emulation for PUshdown Model), a binary analyzer concentrating on malware for Intel x86 architecture. Learning from its experiences, BE-PUM can be extended to other platforms. By considering IoT Malware, ARM is our first target.

ARM is a family of computer processors, acts as the architecture behind billions of devices, especially IoT devices. The explosive growth of IoT devices leads to the rapid increase of IoT malware. With a huge number of connected devices worldwide, IoT malware can infect quickly from a device to others among the network. After the infection, their collaboration might cause dangerous large-scale attacks (e.g., BotNet). As our observation, even IoT malware is lightweight, it still contains obfuscated code. To overcome this problem, DSE should be applied to efficiently reconstruct the Control Flow Graph of IoT malware. After that, the generated CFG can be used to correctly trace behaviors of malware then proceed detection and classification tasks. However, ARM architecture consists of various series such as Cortex-M, Cortex-A, and Cortex R. Due to the huge number of instructions for each series, manual implementation of the Dynamic Symbolic Execution for ARM requires a lot of engineering efforts. As the result, a method to semi-automatically extract the semantics of ARM is essential and meaningful.

Based on our observation from the official ARM developer website, the ARM instructions have been written by natural language in English with some specific information such as mnemonic, operation specifications, and flags-update descriptions. Through our investigation, these descriptions frequently use some particular phrases, which can be extracted by using some Natural Language Processing techniques. Therefore, it is feasible to systematically extract formal semantics of ARM instructions from these documents. After that, the binary emulator and path conditions can be also generated, which will be used in the Dynamic Symbolic Executor for ARM. By semi-automatically generating from Natural Language Specifications, this procedure saves a lot of human efforts. However, the lack of pseudo-code in the description of operations is a big challenge, and the various type of flags-update description also makes some difficulties to analyze.

This thesis proposes an efficient method to systematically extract the formal semantics of ARM instructions from their natural language specifications over six Cortex series: Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, and Cortex-M33. Although ARM is based on RISC architecture and the number of instructions is rather small, a large number of variations exist under Cortex-A, Cortex-M, and Cortex-R. Thus, automatic extraction of the formal semantics of rather simple instructions reduces the human effort for tool development, such as the dynamic symbolic execution. We focus on 6 variations, M0, M0+, M3, M4, M7, and M33 of ARM Cortex-M, aiming to cover IoT malware. By preparing 205 semantics interpretation rules (and additional 23 syntax normalization rules) on phrases, we have automatically extracted the formal semantics of 692 instructions have passed the automated conformance testing. With 35 manually implemented default methods, a dynamic symbolic execution tool for ARM Cortex-M variations has started to work. Because our proposed method is a generalized approach, it can be quickly extended to other platforms without a lot of modifications.

**Keywords:** Semantics Extraction, IoT Malware, ARM Cortex-M, Dynamic Symbolic Execution, Natural Language Processing.

# Acknowledgment

First and foremost, I wish to express my sincere gratitude and respect to my supervisor, Professor Mizuhito Ogawa for his continuous supports and kindly guidance during my study at Japan Advanced Institute of Science and Technology. He has inspired me to become a scientific researcher, as well as given me invaluable knowledge of how to deal with problems and how to think critically. While I was completing this thesis, even at very late night, he still spent several hours to discuss and gave me lots of comments. I am very thankful about that.

Besides, I would like to say my special thanks to my second supervisor, Associate Professor Nao Hirokawa for his useful advice and sharp comments for my research. He also gave me many suggestions for the slides and contents of my presentation, which actually helps me a lot to improve my work.

I would like to express my appreciation to my friends, Dr. Vu Xuan Tung, Mr. Nguyen Lam Hoang Yen, Ms. Vuong Thi Hai Yen, Mr. Trac Quang Thinh, and Ms. Yoon Myet Thwe. Thank you for sharing wonderful moments, interesting ideas, and useful experiences not only in research but also in daily life. I will never forget our Kimono lab, absolutely. My thank also goes to Mr. Le Khanh Trinh, for helping me a lot since the very first day I came to JAIST.

Last but not least, my family is an indispensable part of my life. There are no proper words to express how much important they are. Their big love and encouragement motivated me to study and keep moving forward. I would like to give my heartfelt thanks to my dear father, mother, and sister. Without their support, it would be impossible for me to complete this work.

# Contents

| 1        | Intr | oductio | on                                                    | 1  |

|----------|------|---------|-------------------------------------------------------|----|

|          | 1.1  | Motiva  | ation                                                 | 1  |

|          | 1.2  | Proble  | m Statement                                           | 3  |

|          | 1.3  | Related | d Work                                                | 8  |

|          | 1.4  | Contril | butions                                               | 9  |

|          | 1.5  | Thesis  | Structure                                             | 9  |

| <b>2</b> | Pre  | liminar | ries                                                  | 11 |

|          | 2.1  | Natura  | al Language Processing Techniques                     | 11 |

|          |      | 2.1.1   | Sentence Syntax Parsing                               |    |

|          |      | 2.1.2   | TF-IDF Score                                          |    |

|          |      | 2.1.3   | Cosine Similarity Measure                             |    |

|          | 2.2  | Machir  | ne Learning Techniques                                | 15 |

|          |      | 2.2.1   | Probabilistic Distributions                           |    |

|          |      | 2.2.2   | Latent Dirichlet Allocation                           |    |

| 3        | юТ   | Malwa   | are Analysis                                          | 20 |

| -        | 3.1  |         | cation Techniques                                     |    |

|          | 3.2  |         | al Approaches                                         |    |

|          | 3.3  |         | are Analysis Based on Control Flow Graph              |    |

|          |      | 3.3.1   | Dynamic Symbolic Execution                            |    |

|          |      | 3.3.2   | On-the-fly CFG Generation                             |    |

|          |      | 3.3.3   | BE-PUM for x86/Windows                                |    |

| 4        | AR   | M Forr  | mal Semantics                                         | 29 |

| _        | 4.1  |         | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | -  |

|          | 1.1  | 4.1.1   | Architecture                                          |    |

|          |      | 4.1.2   | Cortex Series                                         |    |

|          |      | 4.1.3   | Instructions                                          |    |

|          | 4.2  |         | l Semantics of ARM                                    | -  |

|          | 1.2  | 4.2.1   | Abstract Environment                                  |    |

|          |      | 4.2.2   | Operational Transitions                               |    |

|          |      | 4.2.3   | Java Specifications as Semantics                      |    |

|          | 4.3  | -       | tics Extraction Overview                              |    |

| <b>5</b> | Syntax Normalization and Semantics Interpretation | <b>42</b> |

|----------|---------------------------------------------------|-----------|

|          | 5.1 Instructions Normalization                    | 42        |

|          | 5.2 Automatic Instructions Selection              | 46        |

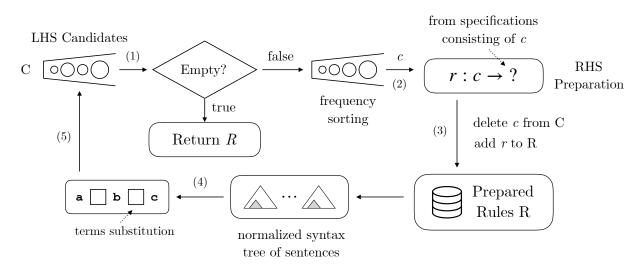

|          | 5.3 Rewriting Rules Preparation                   | 48        |

| 6        | Dynamic Symbolic Executor Generation              | 51        |

|          | 6.1 Generation Overview                           | 51        |

|          | 6.2 Operations Code Generation                    | 52        |

|          | 6.3 Flags Update Detection                        | 54        |

|          | 6.4 Path Conditions Generation                    | 56        |

| 7        | Conformance Testing                               | <b>59</b> |

|          | 7.1 Automatic Tests Generation                    | 59        |

|          | 7.2 Test Case Structure                           | 61        |

|          | 7.3 Testing Procedure                             | 61        |

| 8        | Experiments                                       | 63        |

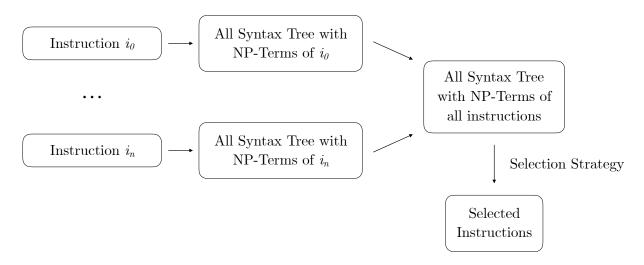

|          | 8.1 Instruction Selection Strategy                | 63        |

|          | 8.2 Successfully Generated Instructions           | 64        |

|          | 8.3 Discussion                                    | 65        |

|          | 8.4 Running Example of the Generated DSE Tool     | 66        |

| 9        | Conclusion and Future Directions                  | 68        |

|          | 9.1 Result and Conclusion                         | 68        |

|          | 9.2 Future Directions                             | 69        |

#### Bibliography

This dissertation was prepared according to the curriculum for the collaborative education program organized by Japan Advanced Institute of Science and Technology and University of Engineering and Technology, Vietnam National University.

# List of Figures

| $1.1 \\ 1.2 \\ 1.3$                                                          | A part of ARM Cortex-M7 instruction set                                                                                                                                                                         | $4 \\ 6 \\ 7$                                |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.1                                                                          | An example result of syntax parser                                                                                                                                                                              | 13                                           |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                         | Indirect jump in an IoT malware                                                                                                                                                                                 | 21<br>21<br>23<br>24<br>25<br>26<br>27<br>27 |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \end{array}$ | Components of ARM ArchitecturePopular Cortex series of ARMThe semantics transition framework of ARMThe simplest implementation of CLZThe unfolded form of CLZThe SMT format of CLZSemantics Extraction Overview | 29<br>31<br>34<br>39<br>40<br>40<br>41       |

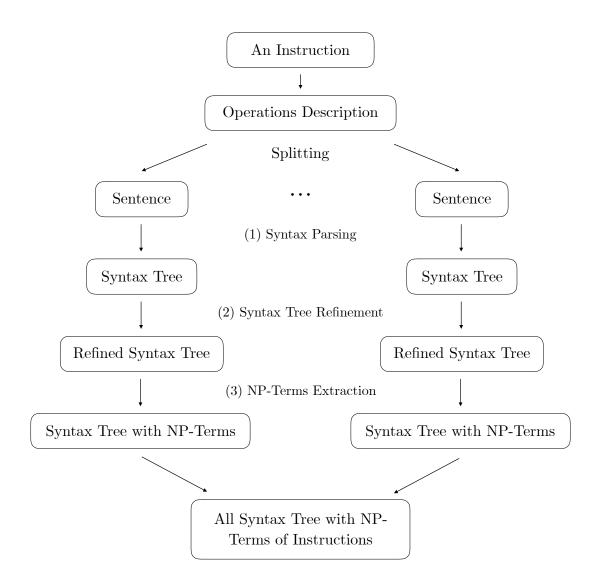

| $5.1 \\ 5.2 \\ 5.3$                                                          | Instruction Normalization Procedure                                                                                                                                                                             | 43<br>44<br>46                               |

| $6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5$                                            | Java code generation overview for an instruction                                                                                                                                                                | 52<br>53<br>54<br>55<br>57                   |

| 7.1<br>7.2<br>7.3                                                            | An example of function need to be tested                                                                                                                                                                        | 60<br>60<br>62                               |

| 8.1 | Instruction Selection Strategy Performance                             | 63 |

|-----|------------------------------------------------------------------------|----|

| 8.2 | An example demonstrating how our DSE generates path conditions through |    |

|     | executions and explores the destination of an indirect jump            | 67 |

# List of Tables

| tion in Cortex-M7 5<br>RM instructions 8    |

|---------------------------------------------|

|                                             |

| architecture                                |

|                                             |

|                                             |

| six Cortex series $\ldots \ldots \ldots 64$ |

| Cortex-M765                                 |

| $rtex-M0+\ldots$ 66                         |

| rtex-M7 $\ldots$ 66                         |

| 4<br>1<br>1<br>1<br>1<br>1<br>1<br>1        |

# Chapter 1 Introduction

## 1.1 Motivation

Malware (shortened of Malicious Software) is a program intending to infiltrate the system without the acceptance of owners, them harm or disable computer systems. By the purpose of how it damages the system, it can be characterized into many types such as worms, virus, trojans, and spyware. The best way to protect the systems against the damages of malware is proactive detection. However, it is not an easy problem because modern malware usually uses many obfuscation techniques [1] in order to conceal its behaviors and protect itself against antivirus software. Therefore, the problems of how to detect and classify malware have been received a lot of attention in the community. There are many existing approaches to do that including static analysis, dynamic analysis, model checking based, and machine learning approach. In almost cases, disassembling binary files is the very first requirement. However, current famous disassemblers (e.g. IDA Pro, Capstone) are easily fooled by obfuscation techniques. To overcome this problem, some model checking based approaches [2] [3] [4] have been applied to first obtains the abstract model of the binary file, then proceed some further methods to detect malware based on the generated model. A typical model has been used is Control Flow Graph (CFG), which is a directed graph to represent the program execution process. Currently, we have developed BE-PUM (Binary Emulation for PUshdownModel), a binary analyzer focusing on x86 malware. It uses the Dynamic Symbolic Execution technique to reconstruct the CFG of malware, then enables us to trace its correct behaviors. By learning from the experiences, BE-PUM can be extended to other architectures, and the first target is ARM.

ARM is a processor family, which is the backbone of billions of devices in the world, especially the IoT devices. Recently, the number of IoT device has raised rapidly. According to a prediction of Statista<sup>1</sup>, the number of IoT devices connected worldwide during the period from 2015 to 2025 will increase from 15.41 to 75.44 billion. This development leads to the fast growth of IoT malware. Different from Intel x86 malware, IoT malware is light-

<sup>&</sup>lt;sup>1</sup>Statista (2018). Internet of Things - the number of connected devices worldwide 2015 - 2025

weight, which can be deployed in many small devices such as smart-phones, routers, and devices in smart-home ecosystems. Although the computing power of each IoT device is low, for a huge number of IoT devices, they can collaborate for making large-scale attacks (e.g., BotNet). Although almost IoT malware does not include obfuscation techniques (due to rare system update), analyzing of indirect jump will be needed to understand its control behavior. To overcome this problem, it is necessary to apply Dynamic Symbolic Execution to reconstruct its Control Flow Graph, then use the generated graphs to perform detection or classification tasks. Dynamic Symbolic Execution technique requires a binary emulator and path constraints generation over each execution. However, ARM architecture has many Cortex series; each one contains an instruction set with plenty of individual instructions. This diversity takes a huge engineering effort to manually implement the Dynamic Symbolic Executor for ARM. Therefore, a method to systematically extract the formal semantics of ARM instructions will be very useful since it saves a lot of human efforts. Our ultimate goal is proposing a method to semi-automatically extract formal semantics of ARM. This method must be generalized for being able to be extended to other architectures without big modifications.

Symbolic Execution [5] is an old, powerful, and popular method to analyze and/or verify software. It has been developed mostly for high-level programming languages, such as Java and C. Recently, the symbolic execution tools for binaries gradually increase, e.g., MiAsm [6], McVeto [7], CoDisasm [8], BE-PUM [9], and KLEE-MC [10], but most of them target on x86. Considering the evolving threat of IoT malware, extending such tools to various instruction sets, e.g., ARM, MIPS, and PowerPC becomes important. The difficulties on handling binaries lie on (1) the operational semantics is intricate to human and (2) the number of instructions is often large, e.g., > 1000 for x86. However, contrary to high-level programming languages, good news are:

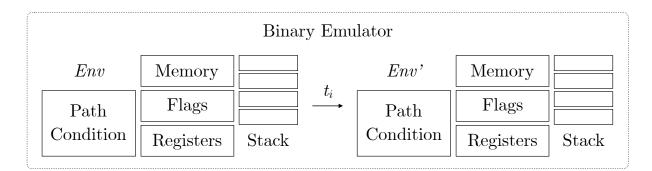

- A binary program has a simple semantics framework as transitions on the environment consisting of a memory, a stack, registers, and flags.

- The instruction set has a rigid natural language specification.

- Since many debuggers and emulation environments are prepared, the ambiguity of natural language specifications can be resolved by testing.

We target on ARM, of which the specifications is available on ARM Developer Website [11]. Since ARM is a RISC-based processor family, it has rather few instructions ( $\simeq 60$  - 300). However, it has three Cortex series: M for microcontrollers (e.g., IoT devices), A for rich operating systems (e.g., Android), R for real-time systems (e.g., LTE modems). Furthermore, each has many variations, e.g., 16 in Cortex-A, 9 in Cortex-M, and 5 in Cortex-R, which are still increasing.

This thesis proposes a method to systematically extract the formal semantics of instructions from their natural language specifications collected from ARM Developer Website. For each instruction, first, we apply some natural language processing techniques to retrieve information of its arguments, its flags updates, and its actions. After that, the formal semantics is described as a Java method in an extension of BitSet class obtained by instantiating these information to a dynamic template. This template represents the semantics framework as a transition on quadruplets of the flags, the registers, the memory, and the stack.

Since the flags update is a boolean operation, a similarity analysis with model sentences often works, e.g., x86 specifications at Intel Developer Network [12]. A more challenging task is the semantics extraction of the actions; different from Intel Developer Network for x86, the specifications at ARM Developer Website does not provide the pseudocode description. We manually prepare rewriting rules as a semantic interpretation that converts a normalized syntax tree of a sentence to a Java code fragment in a bottom-up manner. At last, the generated Java method is automatically tested whether the result matches with a popular ARM emulator, e.g.,  $\mu Vision$  [13].

Note that, instead of intending a fully automatic extraction, we hope to reduce human effort by automatically handling rather simple but many instructions. Then, when developing a formal method tool, human can concentrate only on the most complex part. Our experiment is performed on 6 Cortex-M variations: M0, M0+, M3, M4, M7, and M33. By preparing 205 semantics interpretation rules (and additional 23 syntax normalization rules) on phrases, we have successfully extracted the formal semantics of 692 instructions among 1039 collected specifications, and 662 instructions have passed the automated conformance testing. With 35 manually implemented methods, a dynamic symbolic execution tool for ARM Cortex-M variations has started to work.

# 1.2 Problem Statement

ARM is a RISC based CPU and the number of instructions is relatively small. However, it has many variations call Cortex (e.g., Cortex-A, Cortex-M, Cortex-R). In this research, we focus on Cortex-M series since it was used in plenty of IoT devices. The ARM Developer website<sup>2</sup> provides the natural language specifications of Cortex-M series. Some of them have been written in structured forms with natural language description, some have been written totally in natural language and have been enclosed in a PDF file. In fact, extracting structured data from PDF file is a challenge because we just can gather almost the information by plain text even it is written inside a table in this PDF file. Forming these text into structured data requires a lot of efforts. Therefore, for the first experience, we focus on six series: Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, and Cortex-M33, which are written in structured form.

The table below shows some instructions in the official ARM Cortex-M7 instruction set

<sup>&</sup>lt;sup>2</sup>https://developer.arm.com/

| Mnemonic  | Operands                | Brief description                      | Flags           |

|-----------|-------------------------|----------------------------------------|-----------------|

| AND, ANDS | {Rd,} Rn, Op2           | Logical AND                            | $^{ m N,Z,C,V}$ |

| ASR, ASRS | Rd, Rm, <rs #n></rs #n> | Arithmetic Shift Right                 | -               |

| В         | label                   | Branch                                 | -               |

| BFC       | Rd, #lsb, #width        | Bit Field Clear                        | N,Z,C           |

| BFI       | Rd, Rn, #1sb, #width    | Bit Field Insert                       | N,Z,C           |

| BIC, BICS | {Rd,} Rn, Op2           | Bit Clear                              | -               |

| BKPT      | #imm8                   | Breakpoint                             | -               |

| BL        | label                   | Branch with Link                       | -               |

| BLX       | Rm                      | Branch indirect with Link and Exchange | N,Z,C           |

| вх        | Rm                      | Branch indirect and Exchange           | -               |

| CBNZ      | Rn, label               | Compare and Branch if Non Zero         | -               |

| CBZ       | Rn, label               | Compare and Branch if Zero             | -               |

| CLREX     | -                       | Clear Exclusive                        | -               |

| CLZ       | Rd, Rm                  | Count Leading Zeros                    | -               |

document. The full set can be found on ARM Developer Website for Cortex-M7<sup>3</sup>.

Figure 1.1: A part of ARM Cortex-M7 instruction set

where each instruction has same structures of natural language description including some information as follows:

- Mnemonic: The short name of instruction.

- Brief description: A brief information about the purpose of this instruction.

- Syntax: Main components of instruction syntax, including parameters and preconditions that must be checked before execution.

- **Operation:** This is the most essential part of the instructions, contains some sentences describing how the instruction is explicitly executed.

- Flags update: The update status of flags are described here. It uses many synonyms to explain what flags will be changed after execution such as change, update, modify, and set.

$<sup>{}^{3}</sup>https://developer.arm.com/docs/dui0646/a/the-cortex-m7-instruction-set/instruction-set-summary$

The problem can be stated as follows:

Input: Given an official instruction set document of a Cortex series collected from the ARM developer website (one of Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, and Cortex-M33).

**Output:** Extracting the formal semantics of these instructions, then generate a binary emulator and path conditions that will be used for the Dynamic Symbolic Execution for ARM.

| Mnemonic          | UMAAL                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Brief description | Signed multiply with accumulate long                                                                                                                                                                                                                                                                                                                                                   |  |

| Syntax            | UMAAL{cond} RdLo, RdHi, Rn, Rm                                                                                                                                                                                                                                                                                                                                                         |  |

| Operation         | The UMAAL instruction multiplies the two unsigned 32-bit inte-<br>gers in the first and second operands. Adds the unsigned 32-bit<br>integer in RdHi to the 64-bit result of the multiplication. Adds<br>the unsigned 32-bit integer in RdLo to the 64-bit result of the<br>addition. Writes the top 32-bits of the result to RdHi. Writes<br>the lower 32-bits of the result to RdLo. |  |

| Flags update      | This instruction does not affect the condition code flags.                                                                                                                                                                                                                                                                                                                             |  |

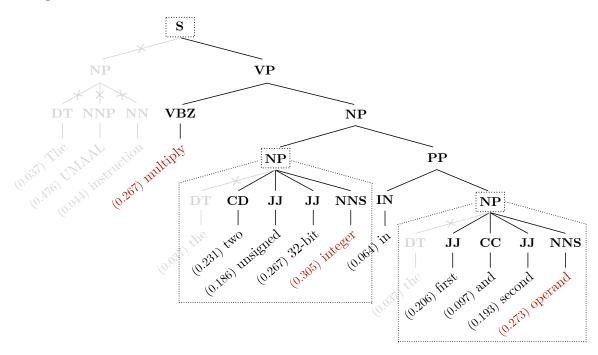

Example 1.2.1. Detailed information of UMAAL instruction in Cortex-M7

Table 1.1: The official description of UMAAL instruction in Cortex-M7

The natural language specification of an ARM instruction taken from ARM Developer Website consists of five sections: *mnemonic*, *brief description*, *syntax*, *operation*, and *flags update*. From these information, we aim to extract this formal semantics

$$R_{pc} = k; instr(k) = umaal \ rdlo \ rdhi \ rn \ rm; R_{rdlo} = lo; R_{rdhi} = hi;$$

$$\frac{R_{rn} = n; R_{rm} = m; a = m * n + lo + hi; hi' = a \gg 32; lo' = (a \ll 32) \gg 32;}{\langle F, R, M, S \rangle \rightarrow \langle F, R[pc \leftarrow k + | \ instr(k) \ |; R_{rdlo} \leftarrow lo'; R_{rdhi} \leftarrow hi'], M, S \rangle}$$

[UMAAL]

by using some sentence-level NLP (natural language processing) techniques: (1) the syntax analysis, (2) the similarity analysis, and (3) the semantic interpretation. The instruction name and arguments are directly extracted from the *syntax* section by (1), the flag update information is extracted from the *flags update* section by (1) and (2), and the actions are extracted from the *operation* section by (1), (2), and (3), ignoring the *mnemonic* and the *brief description* sections.

Our expected output for this example is the Java executable code of UMAAL for Cortex-M7. This code contains the semantics transition of ARM instructions including path condition updates.

```

public void UMAAL (Character 1, Character h, Character n, Character m,

Character suffix, Character cond) {

env.arithmeticMode = ArithmeticMode.BINARY;

if (cond == null || env.checkCond(cond)) {

char[] flags = new char[]{};

BitVec result = null;

result = mul(val(n),val(m));

result = add(result,val(h));

result = add(result,val(1));

write(h, shift(result, Mode.RIGHT, 32));

write(l, shift(shift(result, Mode.LEFT, 32), Mode.RIGHT, 32));

if (suffix != null && suffix == 's') {

if (result != null) {

env.updateFlags(flags, result);

}

}

}

}

```

Figure 1.2: The generated Java code of UMAAL instruction in Cortex-M7

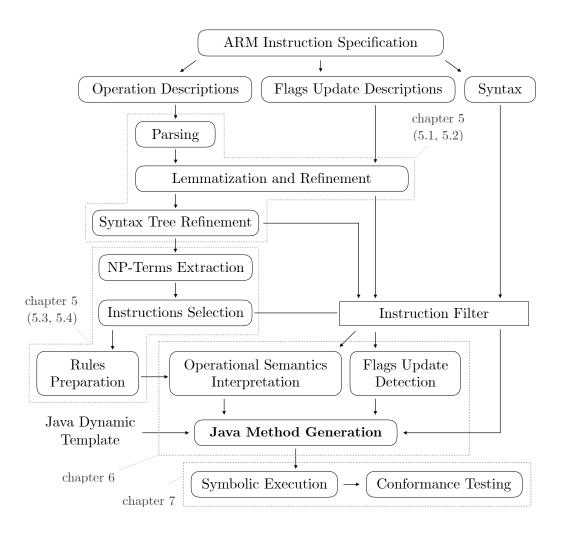

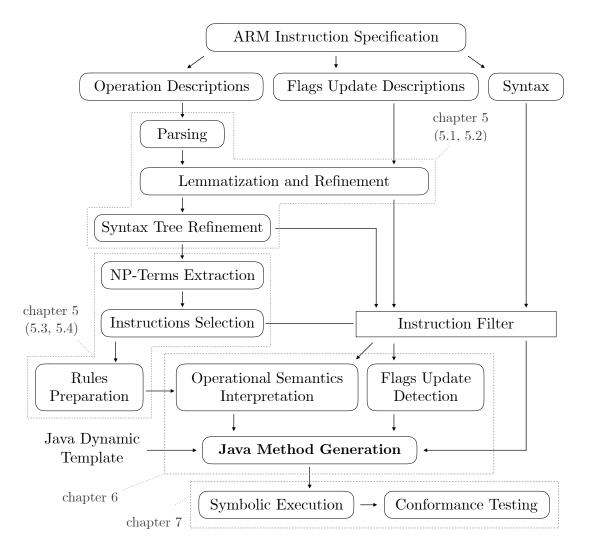

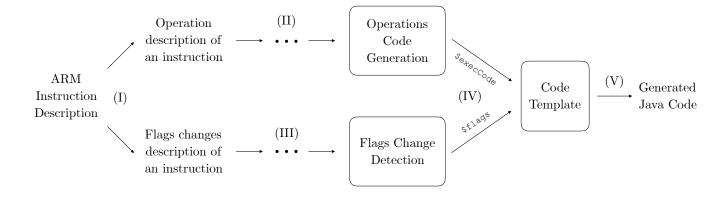

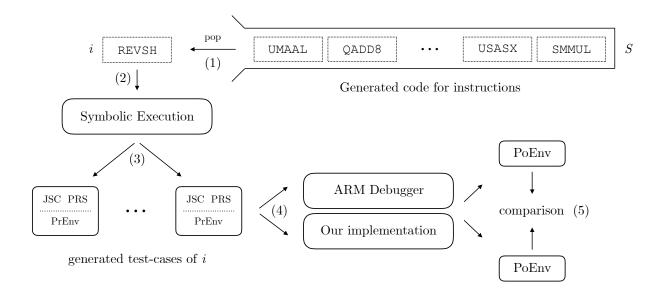

**Solution Overview:** Figure 1.3 shows the flow of our method, in which two are manually prepared:

- (A) 35 initial functions for the binary emulator, which are used as basic methods in the Java dynamic template. Note that, these functions both update the environment and path condition through each transition.

- (B) 228 rewrite rules consisting of 23 syntax normalization rules and 205 semantic interpretations rules where the left-hand sides of rules are collected automatically and the right-hand sides are prepared manually.

To have an optimal performance of the automatic extraction with respect to the manual preparation, we first select some ARM instructions, of which their descriptions consist of frequently appearing phrases. Then, fewer rewrite rules cover more instructions. Currently, the total 228 rewrite rules cover 662 instructions among 1039 collected specifications. As the result, by instantiating extracted information to the Java dynamic template, a method that formally describes the semantics of UMAAL is obtained. The dotted boxes indicate the insertions of the extracted information to the template.

Figure 1.3: The Flow of Semantics Extraction

#### Difficulties

There are two major difficulties compared to x86 instruction specification. First, ARM instruction specifications lack of pseudo-code descriptions. Pseudo-code is an informal description of how the program is executed. It enables human to understand the semantics of program without knowledge of any explicit programming languages. In code generation, pseudo-code plays an important roles in describing the execution process of programs. In the work of Yen et al. [12], the pseudo-code in Intel x86 instructions are quite structured. For ARM instructions, instead of pseudo-code, the operations description is written totally by natural language in English. It makes more challenges to analyze and extract information because of the ambiguity and complex structure of natural language. In addition, the operation's description in ARM consists of many separated sentences, in which some sentences describe an operation. Moreover, it may use the result from the previous operation. Hence, to combine all sentences and transform it to a formal unified operation is also a challenge.

In addition, flags changes are also described by natural language only. The table below shows some kinds of expressions for flags-change description.

| Description                                                                           | Implication                                   |

|---------------------------------------------------------------------------------------|-----------------------------------------------|

| This instruction does not change the flags                                            |                                               |

| This instruction does not affect the condition code flags                             | Does not update flags                         |

| The V flag is left unmodified.                                                        | Does not update hags                          |

| This instruction updates the N, Z, C and V flags according to the result.             | Update specific flags<br>based on description |

| Updates the N and Z flags according to the result. Does not affect the C and V flags. |                                               |

Table 1.2: Typical flags modification description of ARM instructions

As for Intel x86 instruction description, ARM also uses many different types of synonyms to describe flags-change. It makes more challenging to correctly detect how flags are affected after execution. Naturally, many synonyms can be used in order to describe such implications. For instance, two sentences "The V flag is left unmodified" and "This instruction does not affect the V flag" have different words, but indicate the same meanings.

# 1.3 Related Work

There are several model checking based approaches [2, 3, 4] to analyze malware. Different from high-level programming languages, binary code is not easy to obtain its control flow graph (corresponding to the difficulty of the disassembly). Thus, before model checking, the precise model needs to be prepared. Recently, the symbolic execution tools for binaries gradually increase, e.g., MiAsm [6], McVeto [7], CoDisasm [8], BE-PUM [9], and KLEE-MC [10], but most of them are for x86. Furthermore, KLEE-MC and MiAsm first convert the binary code to intermediate assembly languages, like LLVM. Although current IoT malware rarely uses typical obfuscation techniques [1] of PC malware, it uses indirect jumps quite often. The traditional disassemble techniques like the *linear sweep* and the recursive disassembling (used in IDA Pro [14], Capstone [15]) are easily cheated by them. The use of intermediate assembly languages shares the problem. The symbolic execution of CoDisasm relies on MiAsm and has difficulties on handling indirect jumps. BE-PUM and McVeto on x86 directly apply the symbolic execution on binaries (with the one-step disassembly at the specified address) to handle indirect jumps precisely. The difference is that McVeto uses only the symbolic execution and the destination candidates of indirect jumps are analyzed statically, whereas BE-PUM uses the dynamic symbolic execution and the destinations of indirect jumps are decided by the concolic testing. Thus, the targets of McVeto is mostly limited to compiled binaries. We follow the same methodology of BE-PUM, but apply it to ARM Cortex-M.

The drawback of the methodology is that the implementation becomes heavy. Thus, we hope to have an automated support to extract the formal semantics of binary instructions. For a wider coverage of BE-PUM, the semantics extraction from the x86 specifications collected from Intel Software Developer's Manual has been tried [12]. It covered 299 x86 instructions among 530 collected specifications, and the 5 semantic bugs in the manual implementation of BE-PUM are reported. It relies on the pseudo code description for extracting the information of the actions (with the aid of manually implemented about 30 functions), and the similarity analysis using a sophisticated scoring based on WordNet [16] is an essential use to extract the information of the flags update. In our case, the specification of ARM does not have such a pseudocode description and we need to use the semantics interpretation.

## **1.4** Contributions

The specification of ARM instructions is written in English by natural language. This study focuses on analyzing and extracting formal specification from natural language description over six cortex series. Because of the ambiguity of natural language, it is not a straightforward task. Our main contributions consist of:

- First, we proposed a generalized method to extract the semantic of operations in instructions, then generate its formal executable code (represented in Java). This method can be extended to multiple platforms, as long as the rewriting rules for each platform are defined correctly. In this method, we also introduce a strategy for automatically select potential instructions to optimize the needed human efforts for implementation. In this method, we also provide a set of rewriting rules for ARM Cortex-M series, which can be modified for extending to other architectures.

- Second, we present an approach to automatically detect the flags-changes using an unsupervised learning algorithm called Latent Dirichlet Allocation and the Cosine similarity measure.

- Finally, we combine two methods above to develop a tool to completely generate the formal semantics of ARM instructions. In our work, this formal specifications are written in Java, consisting of both path conditions update and a binary emulator. This semantics which will be further used in the Dynamic Symbolic Execution for ARM.

## 1.5 Thesis Structure

This thesis is organized into nine chapters. Chapter 1 is the introduction; the main content of the next eight chapters are summarized as follows:

- Chapter 2 presents some background knowledge of Natural Language Processing and Machine Learning techniques that are applied in the scope of this thesis.

- Chapter 3 briefly introduces IoT malware and typical approaches of malware analysis. Besides, it also presents the approach to overcome obfuscation techniques called Dynamic Symbolic Execution (concolic testing) and the current tool BE-PUM for x86/Windows.

- Chapter 4 first briefly talks about ARM architecture, then introduces the formal semantics of ARM, including both operational semantics and Java semantics. It also shows an overview of semantics extraction process.

- Chapter 5 mentions about some prerequisites needed to be done before the semantics extraction process. It also illustrates how the potential instructions is selected and how we prepared rewriting rules for further generation task.

- Chapter 6 explains how the dynamic symbolic executor for ARM is systematically generated. The generation process includes three tasks: operation code generation, flags change detection and path condition generation.

- Chapter 7 presents a conformance testing method to verify the correctness of our implementation using Symbolic Execution.

- Chapter 8 shows the practical experiments result over six Cortex series of ARM architecture, including the instruction selection strategy, and the generated instructions. In addition, some cases that still cannot be covered are discussed. Finally, a running example of the generated DSE tool is also demonstrated.

- Chapter 9 summarizes the main contributions of the thesis and the advantages as well as remaining drawbacks. After that, some future works are also mentioned to suggest some directions to improve and extend our proposed method to other platforms.

# Chapter 2 Preliminaries

This chapter presents some existing techniques used in our method. For extracting formal semantics of ARM, Natural Language Processing techniques are used to process text data collected from ARM Developer Website and perform the instruction normalization. We also use a Machine Learning algorithm called Latent Dirichlet Allocation for detecting flags modifications.

# 2.1 Natural Language Processing Techniques

In computer science, Natural Language Processing (NLP) is a research field that aims to enable computers to understand and be able to communicate with human by natural language. It is one of the indispensable factors for the interaction between human and machine. Recently, the increase of computing power and the availability of big data leads to the rapid growth of NLP. Some typical advanced problems in NLP are information extraction, machine translation, text summarization, and text generation. Applying NLP to automatically extract information from text has been received a lot of attention from the community because it saves a lot of human efforts. As our observation, this technique can be used to extract formal specification of ARM instruction from its natural language description. In this work, Syntactic Parser, TF-IDF score, and Cosine similarity have been applied.

#### 2.1.1 Sentence Syntax Parsing

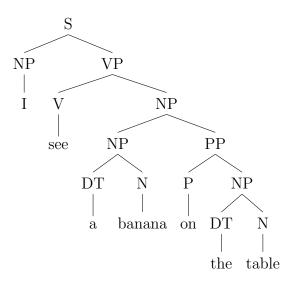

Syntax Parsing (known as Parsing for short) is a process to determine the syntactic structure of a sentence based on a given formal grammar. This technique has been widely used as the pre-processing task of many natural language processing algorithms before proceeding next steps. It inputs a sentence and a grammar, then outputs a syntax tree which represents the syntax of this sentence. The grammar used in Parsing can be a context-free or domain-oriented grammar. In this study, we used a context-free grammar.

**Definition 2.1.1.** A context-free grammar G is a reduction system over strings that uses a set of rules to rewrite string patterns. It consists of four components  $\langle N, T, R, S \rangle$  where:

- N: a set of non-terminal symbols.

- T: a set of terminal symbols.

- R: a set of rewriting rules. Each rule is denoted as  $a \to b$ , where a, b are strings.

- S: a set of start symbols. Each element of S is a non-terminal symbol.

A syntax tree of a sentence S now will be generated by performing rule matching by replacing the left-hand side by the right-hand side of rules until the right-hand side contains only terminal symbols.

**Example 2.1.1.** Consider a context-free grammar G as follows:

```

S \rightarrow NP VP

PP \rightarrow P NP

NP \rightarrow DT N | DT N PP | 'I'

VP \rightarrow V NP | VP PP

DT \rightarrow 'a' | 'the'

N \rightarrow 'banana' | 'table'

V \rightarrow 'see'

P \rightarrow 'on'

...

```

where:

| Notation | Meaning     | Notation | Meaning              |

|----------|-------------|----------|----------------------|

| S        | Sentence    | PP       | Prepositional Phrase |

| NP       | Noun Phrase | DT       | Determiner           |

| VP       | Verb Phrase | Р        | Prepositional        |

| V        | Verb        | Ν        | Noun                 |

Table 2.1: Syntax notations in the grammar G

In this case, the components of G are:

- N: NP, PP, VP, DT, ...

- T: 'a','on','see','banana', ...

- R: S  $\rightarrow$  NP VP, PP  $\rightarrow$  P NP,  $\ldots$

- S: S, ...

Then, a syntax tree of the sentence "I see a banana on the table" based on G is:

Figure 2.1: An example result of syntax parser

#### 2.1.2 TF-IDF Score

Term Frequency - Inverse Document Frequency (TF-IDF) is a measure to estimate the importance of a word to a document over a corpus. It is usually used in text mining to refine sentences for the preprocessing task. Besides, it has been also applied to calculate the similarity between two document by using cosine distance between two sentence's TF-IDF vector. In this work, TF-IDF was used as an evaluation to remove unimportant words, acts as a pre-processing task. The reason why this task is essential is that almost unimportant words do not carry the meaning of the sentence. It can be removed to shorten the sentence and make it simpler. It is useful for the next steps of generating rewriting rules. The input of this task is a target document d and a corpus D. It outputs a real numbers vector that represents the score of each word in d.

**Definition 2.1.2.** Given a set of n documents:

$$D = \{d_1, d_2, d_3, \dots, d_{n-1}, d_n\}$$

(2.1)

Each document *i* is a set of  $m_i$  words:

$$d_i = \{w_1^i, w_2^i, w_3^i, \dots, w_{m_i-1}^i, w_{m_i}^i\}$$

(2.2)

Then:

• Term frequency of  $w_k^i$  is defined as:

$$tf(w_k^i) = \frac{f_{d_i}^k}{m_i} \tag{2.3}$$

• Inverse document frequency of  $w_k^i$  is defined as:

$$idf(w_k^i) = \log_e(\frac{n}{f_D^{w_k^i}}) \tag{2.4}$$

• TF-IDF of  $w_k^i$  is defined as:

$$tfidf(w_k^i) = tf(w_k^i) \times idf(w_k^i)$$

(2.5)

where:

- $f_{d_i}^k$ : The number of occurrences of  $w_k^i$  in  $d_i$ .

- $f_D^{w_k^i}$ : The number of document in *D* containing  $w_k^i$ .

The  $tfidf(w_k^i)$  can represent the importance of a word  $w_k^i$  in the document  $d_i$  because:

- 1. If  $w_k^i$  appears many times in  $d_i$ , it is important for  $d_i$ . The bigger number of occurrences, the bigger  $tf(w_k^i)$ . It will led to the increment of  $tfidf(w_k^i)$ .

- 2. On a other hand, if  $w_k^i$  also appears many times in D, it is so common. The bigger number of occurrences, the smaller  $idf(w_k^i)$ . It will led to the decrement of  $tfidf(w_k^i)$ .

#### 2.1.3 Cosine Similarity Measure

Cosine similarity is a real value reflecting the difference of two non-zero vectors based on the cosine of its spatial angle. To apply Cosine similarity for determining whether the semantic of two sentences are equivalent or not, we first need to transform two sentences  $s_1$ ,  $s_2$  into two non-zero vectors  $v_1$ ,  $v_2$ , respectively. Then the value of Cosine Similarity between  $v_1$  and  $v_2$  is the distance between  $s_1$  and  $s_2$ .

**Definition 2.1.3.** Let  $v_a$  and  $v_b$  are two non-zero real vectors with n dimensions:

$$v_a = (a_1, a_2, a_3, \dots, a_{n-1}, a_n)$$

$v_b = (b_1, b_2, b_3, \dots, b_{n-1}, b_n)$

The Cosine similarity between  $v_a$  and  $v_b$  is defined by:

$$sim(v_A, v_b) = \frac{v_a \cdot v_b}{\|v_a\| \|v_b\|} = \frac{\sum_{i=1}^n a_i b_i}{\sqrt{\sum_{i=1}^n a_i^2} \sqrt{\sum_{i=1}^n b_i^2}}$$

(2.6)

# 2.2 Machine Learning Techniques

Machine Learning (a branch of Artificial Intelligence) is a set of algorithms that enables machines to automatically learn from previous experiences and after that, it can be able to adapt and predict new unseen data. Recently, Machine Learning is regularly used in many problems such as classification, regression, clustering, and detection. In fact, Machine Learning can be combined with other technologies to create more efficient algorithms for analyzing a huge amount of information. Based on how the machine learning algorithms "learn" from data, it can be classified into the following categories:

- Supervised learning algorithm: This is the algorithm which uses labeled training data to learn a generalized model, then uses this model to predict unlabeled testing data. Some famous supervised learning algorithms are Support Vector Machine, Neural Networks, Decision Tree, and Linear Regression.

- Unsupervised learning algorithm: Opposite to supervised learning algorithms, this kind of algorithm uses the unlabeled data to learn a generalized model for describing a latent structure behind the data. Although it cannot figure out the label of data, it still can divide data into some clusters. Some popular algorithms are K-means, K-nearest Neighbor, and Latent Dirichlet Allocation.

- Semi-supervised learning algorithm: This kind of algorithm uses both labeled and unlabeled data for the training process. Basically, it is used when we have a large set of unlabeled data and a small set of labeled data. In this case, labeled data will be used to improvement the accuracy of training process.

- *Reinforcement learning algorithm:* In some specific situation, the machine learning algorithm need to interact and adapt to its environment (e.g., games' AI bot). It uses the feedback and errors from the environment to improve itself, then after that, it can make better decisions.

In our works, a probabilistic unsupervised machine learning model called Latent Dirichlet Allocation (LDA) has been applied to represent a document by a distribution of topics. The basic idea of LDA is that each document is considered as a distribution of hidden topics d where each topic is a distribution of words. Then LDA tries to figure out d based on the training data.

#### 2.2.1 Probabilistic Distributions

A probability distribution is a function describing the proportion of random variables that occurs in an event. For example, in the coin flipping scenario, assume the coin is fair, the probabilities of *head* and *tail* would be 0.5, 0.5 respectively. It follows the Bernoulli distribution with the  $\lambda = 0.5$ . This section briefly introduces some probabilistic distributions used in the machine learning model that has been applied in our proposed method.

#### **Poisson Distribution**

Poisson Distribution is a discrete probability distribution, describes the average number of successful occurrences of an event e over a given time period t. Consider a random discrete variable N, if the average number of occurrences of N over t is  $\lambda$ , the probability of e occurs k times (k is a non-negative integer) is defined by:

$$p(k;\lambda) = \frac{\lambda^k e^{-\lambda}}{k!} \tag{2.7}$$

where  $e \approx 2.71828$  (Euler's number)

#### **Categorical Distribution**

In many cases, the output of discrete random variables may be one value in a finite set. For example, when you roll a dice, the receiving face is one value in the set  $\{1, 2, 3, 4, 5, 6\}$ . In this case, we usually use Categorical distribution to describe random variables. Assume there are N possible outcomes, the outputs would be described by one element in the set  $\{1, 2, ..., N\}$ . Then, the Categorical Distribution is described by N non-negative parameters:

$$\lambda = (\lambda_1, \lambda_2, \dots, \lambda_N) \tag{2.8}$$

where:

$$\begin{cases} \lambda_i \ge 0\\ \sum_{i=1}^N \lambda_i = 1 \end{cases}$$

(2.9)

Each  $\lambda_i$  represents the probability of output to be *i*:  $p(x = i) = \lambda_i$ . The probability density function of Categorical Distribution is defined as:

$$p(x) = Cat_x[\lambda] \tag{2.10}$$

#### **Dirichlet Distribution**

Dirichlet Distribution is used to describe the parameters of Categorical Distribution. It describes N continuous random variables  $\lambda_1, \lambda_2, \ldots, \lambda_N$ , where

$$\begin{cases}

\lambda_i > 0 \\

\sum_{i=1}^N \lambda_i = 1

\end{cases}$$

(2.11)

17

Using N positive parameters used to describe a Dirichlet Distribution:  $\alpha_1, \alpha_2, \ldots, \alpha_N$ , the probability density function is defined by:

$$p(\lambda_1, \lambda_2, \dots, \lambda_n) = \frac{\Gamma(\sum_{n=1}^N \alpha_n)}{\prod_{n=1}^N \Gamma(\alpha_n)} \prod_{n=1}^N \lambda_n^{\alpha_n - 1}$$

(2.12)

where:

$$\Gamma(z) = \int_0^\infty t^{z-1} \exp(-t) dt$$

(2.13)

For short, it can be written as:  $p(\lambda_1, \lambda_2, \dots, \lambda_k) = Dir_{\lambda_1, \lambda_2, \dots, \lambda_k}[\alpha_1, \alpha_2, \dots, \alpha_K]$

#### 2.2.2 Latent Dirichlet Allocation

In order to extract the characteristics of documents, in information retrieval and data mining, modeling the documents is an essential task before proceeding next steps. Compare to the words vectorization methods, documents represented by probabilistic distribution has many advantages. Latent Dirichlet Allocation (LDA) [17] is a generative probabilistic model over discrete data, which aims to discover the "hidden topics" in a corpus. In LDA, each document is represented by a distribution of hidden topics and a topic is a distribution of words. Because LDA is a bag-of-words model, the order of words does not matter. Beside being applied in text mining, it also is used in many other domains as long as the purpose is to capture the hidden structure of the dataset.

#### Notation

Assume we have a vocabulary  $\vartheta$ , indexed by  $\{1, 2, \dots, V\}$ .

A word is an element from  $\vartheta$ , is represented by an one-hot vector. It means the vword is defined by a vector  $w = (w^1, w^2, \ldots, w^V)$ , in which  $w^i = 1$  if i = v, otherwise,  $w^i = 0$ . A *document* w is represented by a vector of N words, in which  $w_i$  is the *i*th word in the document:

$$w = (w_1, w_2, \dots, w_N)$$

(2.14)

A corpus (or collection) is a set of M documents:

$$D = \{w_1, w_2, \dots, w_M\}$$

(2.15)

#### Assumption

We need to assume a fixed number of topics, say K. Then we have K topics:

$$T = \{t_1, t_2, \dots, t_k\}$$

(2.16)

Then assume the generation of document w in D follows these step:

1. First, decide the number of words N for D according to a Poisson distribution:

$$N \sim Poisson(\xi)$$

2. Second, choose a mixture of K topics for w according to a Dirichlet distribution:

$\theta \sim Dir(\alpha)$

- 3. Third, we next generate each words  $w_i$  in w by:

- Pick a topic according to the multinomial distribution chosen in the second step:  $t_i \sim Multinomial(\theta)$

- Then use this chosen topic above to generate a word  $w_i$  according to a multinomial probability on the topic  $t_i$

Then, LDA tries to learn the topic distribution of each document, and the words associated for each topics. The learning process is performed as follows:

- 1. For all document w in D, assign each word  $w_i$  in w to a random one in K topics.

- 2. After this step, we already have topic distribution of all  $w_i$ , and word mixtures of all topic. But this result is still not good. We need to improve it by performing some iterations:

- For all document w in D:

- For all word  $w_i$  in w:

- For each topic  $t_j$ :

- Calculate:

$$p = p(t_j \mid w) . p(w_i \mid t_j)$$

where

$- p(t_j \mid w)$ : the proportion of words  $w_k$  in w in which  $t(w_k) = t_j$

$- p(w_i | t_j)$ : the proportion of document in D containing  $w_i$  in which  $t(w_i) = t_j$ .

After that, the  $w_i$  is assigned to the topic  $t_j$  with the new probability p.

After some iterations, when the state of the dataset is quite stable, the training can be stopped after some specific iterations or when the perplexity of model is good enough. This model now can be used for inferring topics distribution of a document.

**Example 2.2.1.** Assume we have following sample documents:

- $s_1$ : I love eating apple when walking with my dog at night.

- $s_2$ : I like some sports such as basketball, tennis, and walking.

- $s_3$ : My dog and her cat are playing with the balls.

•  $s_4$ : Today we have apple, orange, and kiwi for a tea break after the tennis match.

Assume we choose the number of hidden topics that need to be discovered is 3 and each topic is a distribution of keywords such as:

- $t_1$ : apple (0.25), orange (0.2), kiwi (0.18), sports (0.1), dog (0.05), cat (0.04), ...

- $t_2$ : dog (0.4), cat (0.3), apple (0.15), basketball (0.05), ...

- $t_3$ : walking (0.35), basketball (0.2), tennis (0.2), orange (0.1), cat (0.05), ...

In fact,  $t_1, t_2, t_3$  are hidden topics. It means we do not know exactly the label of them. However,  $t_1$  could be interpreted as "*fruit*",  $t_2$  could be interpreted as "*animal*", and  $t_3$  could be interpreted as "*sport*". Now, each sentence  $s_i$  can be represented as a distribution of topics:

- $s_1$ :  $t_1$  (0.4),  $t_2$  (0.3),  $t_3$  (0.3)

- $s_2$ :  $t_1$  (0.1),  $t_2$  (0.1),  $t_3$  (0.8)

- $s_3$ :  $t_1$  (0.1),  $t_2$  (0.75),  $t_3$  (0.15)

- $s_4$ :  $t_1$  (0.8),  $t_2$  (0.05),  $t_3$  (0.15)

# Chapter 3

# IoT Malware Analysis

To satisfy the low power requirements, IoT devices tend to use lightweight processors. The most popular processor is being used is ARM. As the result, IoT malware is typically based on ARM architecture. Even though IoT Malware is not much complex as x86/windows malware, by our investigation, it also contains obfuscation techniques in order to hide its behaviors. It leads to some difficulties in detection and analysis because we cannot correctly trace its execution with commercial disassemblers like IDA Pro [14] and Capstone [15].

## 3.1 Obfuscation Techniques

Being obfuscated makes more difficulties for disassemblers to correctly trace the assembly code of malware. As a result, it has more opportunities to survive. Even commercial disassemblers like IDA Pro and Capstone are robust, they are still easily fooled by obfuscation technique such as indirect jump and overlapping instruction. In this section, we present some typical obfuscation techniques frequently appearing in IoT malware.

#### Indirect Jump

An indirect jump (also known as an indirect branch) is a control instruction, in which, instead of clearly determining the next instruction to be executed by an address, the target address is encoded itself and stored indirectly in memory or general-purpose register. Unless the instruction is executed, the specific value of the address to be jumped is unknown. The example below shows an indirect jump in an IoT malware 48cff3f21c provided by Prof. Katsunari Yoshioka (Yokohama National University). At 9a50, the bx instruction executes a jump operation to the address specified by the value stored in the register lr. To deal with this technique, it is necessary to use a binary emulator to get this specific value.

| 9a48:          | e24bd00c | sub sp,fp,#12                          |

|----------------|----------|----------------------------------------|

| 9a4c:          | e89d6800 | ldm sp,{fp,sp,lr}                      |

| 9a50:          | e12fff1e | bx lr                                  |

|                |          |                                        |

| 9a54:          | ela0c00d | mov ip,sp                              |

| 9a54:<br>9a58: |          | <pre>mov ip,sp push{fp,ip,lr,pc}</pre> |

Figure 3.1: Indirect jump in an IoT malware

#### **Dead Code Insertion**

This is a simple technique to modify the structure and appearance of malware, but does not affect its semantic and behaviors. By modifying itself code, it works quite well to protect against some traditional detection method in typical commercial antivirus software like bit-based signatures. In this technique, some ineffective instructions were inserted between the original instructions, then make the assembly code seems more complex, but actually it plays no role in the behavior of malware.

|       |                  | d138: | add r3,r3,r0     |

|-------|------------------|-------|------------------|

|       |                  | d13c: | nop              |

| d138: | add r3,r3,r0     | d140: | add r4,r3,#7     |

| d13c: | add r4,r3,#7     | d144: | mov r5,#5        |

| d140: | mov r5,#5        | d148: | bl 8ecc          |

| d144: | bl 8ecc          | d14c: | add r5,#1        |

| d148: | bcs d5c4         | d150: | sub r5,#3        |

| d15c: | ldr r5,[fp,#-56] | d154: | bcs d5c4         |

| • • • |                  | d158: | add r5,#2        |

|       |                  | d15c: | ldr r5,[fp,#-56] |

|       |                  |       |                  |

Figure 3.2: Original malware assembly code and after dead code insertion

In this figure, we can easily real the problem at d13c, this is a "no-operation" instruction, means that doing nothing here. In addition, at d14c, d150, and d158 the value of the register r5 is modified three times, but after all, the value stored in r5 is unchanged. Although these codes are inserted to make the program more complex, it just can modify the structure, but worths nothing for the behaviors of malware.

## 3.2 Typical Approaches

#### Static Analysis

Static analysis aims to analyze the executable binary files of malware without running it. Some typical methods of static analysis are signature based and behavior based.

- In signature-based approach, the hash value of binary files, or a byte sequence in binary files is used to check whether a new binary file is a malware or not by comparing the signature hash value of this file with the existing hash value stored in a centralized database. This database is regularly updated. This approach is used in many antivirus software because of its light-weight and correctness. But the biggest problems is that the number of unique signatures is huge, as well as modern malware usually use various polymorphic and metamorphic techniques.

- In behavior-based approach, the data flow and control flow of malware are statically explored, then it is used to describe the behavior of malware. These flows are usually represented by directed graphs. Analyzing malware behaviors now becomes checking these graphs. Basically, if malware is totally clear without any obfuscation techniques, this method may work well. However, modern malware is usually obfuscated.

## Dynamic Analysis

Dynamic Analysis aims to analyze malware by actually running it. Based on the specific behavior and the way of how malware affects to the environment during runtime process, we can understand its functionalities and then, explore some indicators as its signature. Some typical indicators are API calls, connected IP addresses or domains, and behavior of downloading some files. Although almost dynamic analysis methods are slower than static analysis, it reflects more precise about malware behaviors. In fact, dynamic analysis and static analysis are usually combined together to improve the accuracy of detection and classification.

### Machine Learning Approach

Malware detection based on Machine Learning approaches are attracting a lot of attention. In the past, when the machine learning model was not robust, and the data set is not big enough, this approach seemed to be inefficient. But currently, many methods gain impressive results. Some typical methods are introduced below:

- Malware as an image: This idea considers a malware as an image, then transforms malware into gray-scale images. After that, by using a Convolution Neural Network (CNN) over transformed images, the detection or classification are performed. For instance, in 2017, Jiawei Su et al. proposed a lightwight classification for IoT malware [18]. His approach converts a binary code to a fixed-size color image and uses AlexNet [19] to perform the classification task.

- Malware as a sequence: This idea considers a malware as a document with a sequence of byte, in which each word is a group of bytes. Then it applies some typical machine learning algorithms to perform the detection or classification. For instance, in 2017, a malware detection from raw byte sequences was introduced by E. Raff et al [20].

This method has a good performance with linear complexity dependence on the length of sequence.

#### Model-checking Based

To make the machine understand and work with real-world systems, it should be simulated by a model in the computer written by logic or mathematics. Malware is not an exception, it usually is represented by a model M, then the all the scenarios and behaviours of M are tested by using formal verification methods. A typical model for binary file is Control Flow Graph (CFG), which reflects its execution steps. After that, the malware classification and detection problems are equivalent to checking the represented model M. Based on model-checking, many algorithms have been proposed to detect malware. For instance, in 2018, Anh Viet Phan et al. introduces a graph-based Convolutional Neural Network approach [21] to perform software defects detection and malware analysis.

### 3.3 Malware Analysis Based on Control Flow Graph

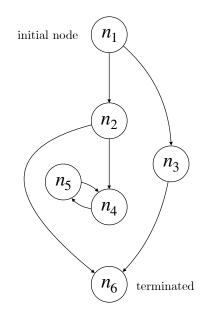

One of the drawbacks of traditional malware analysis methods is that it can not overcome obfuscation techniques. To deal with this problem, Dynamic Symbolic Execution (concolic testing) is applied in order to explore the Control Flow Graph (CFG) of malware. A CFG is a representation model of the program execution process. It is a directed graph which node is a block without any jumps and each edge represents the path condition from the parent node. CFG can explore all feasible paths from the initial state to terminated state during the execution.

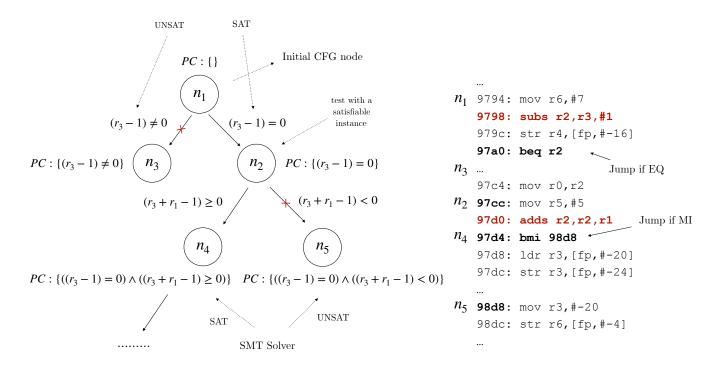

Figure 3.3: A Control Flow Graph of Binary File

This figure above shows an example of CFG. It can be interpreted that, node  $n_1$  and  $n_2$  may causes an if - else statement, node  $n_4$  and  $n_5$  may causes a *while* loop. For binary files, the data instructions such as mov, ldr, add do not affect the jump operations, therefore it can be grouped into a node. If the execution reaches a jump instruction (e.g., b in ARM and jmp in x86), the branch is created by deciding the satisfiability of the current path constrain with a Theorem Prover.

#### 3.3.1 Dynamic Symbolic Execution

Symbolic Execution [5] is a technique has been used regularly in software testing, to execute a program symbolically rather than running it with concrete input values. By using Symbolic Execution, all available scenarios during the execution can be caught. In this technique, inputs are assumed as symbolic values like  $\alpha, \beta$ ; then in every conditional branch, it adds the constraints in the path condition *pc*. By using this approach, the Symbolic Execution can run through all possible path of a program and do the testing all possible outcomes. This technique also is used in software security to detect potential vulnerabilities.

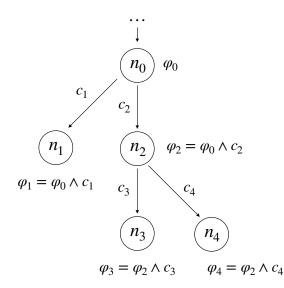

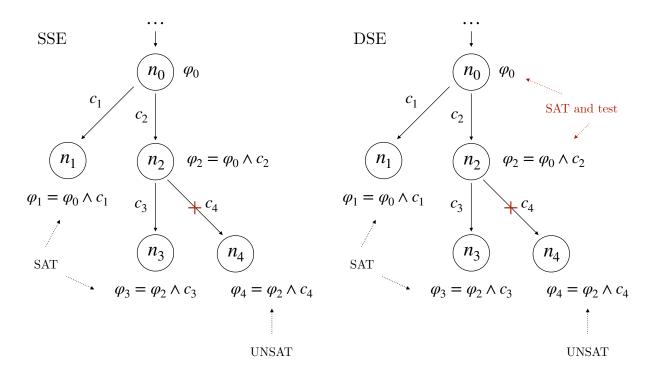

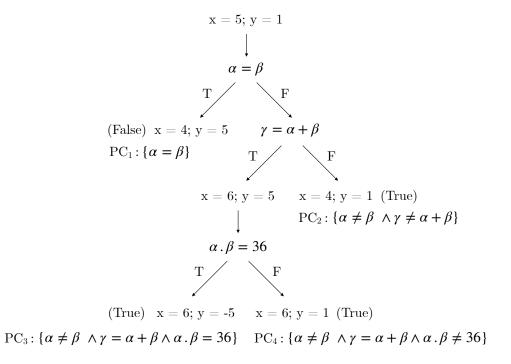

Figure 3.4: Symbolic execution for automatic tests generation

The figure above illustrates how symbolic execution is applied to cover all possible scenarios of a program. Assume the path condition from the initial node of  $n_i$  is  $\varphi_i$ , and the condition from  $n_{i-1}$  to  $n_i$  is  $c_i$ . Then, for each path, the satisfiability of the path condition is checked (e.g,  $\varphi_1$ ,  $\varphi_2$ ,  $\varphi_3$ ,  $\varphi_4$ ) by Z3. If it is SAT, an instance of input values causing this path is collected as a test-case. There are two ways to explore next destinations in Symbolic Execution: Static Symbolic Execution (SSE) and Dynamic Symbolic Execution (DSE).

Figure 3.5: Static Symbolic Execution and Dynamic Symbolic Execution

- Static Symbolic Execution: The next candidates are statically decided by checking the feasibility of each path  $\varphi_2 = \varphi_1 \wedge c_2$ ,  $\varphi_3 = \varphi_1 \wedge c_3$ , and  $\varphi_4 = \varphi_1 \wedge c_4$ . One of the problems of SSE is that, for some specific conditions, the theorem provers cannot easily check the satisfiability of the candidates. For instance, if  $c_2$  keeps the condition: (x \* x \* x + y \* y \* y = z \* z \* z), in which x, y, z are integer numbers, it is really hard to decide whether it is SAT or UNSAT. In this case, the DSE should be used, in which a concrete instance of  $\varphi_0$  should be used in order to test the feasibility of the path.

- Dynamic Symbolic Execution (Concolic Testing): This technique is the combination of concrete execution and static symbolic execution to overcome the drawback mentioned above. I also be used to explore obfuscation techniques like *indirect jump* in malware. In DSE, to decide the next candidates, the feasibility is checked by using a satisfiable instance of  $\varphi_1$ . It requires a binary emulator to get the value of the concrete variables.

To deal with obfuscation techniques in malware like *indirect jump*, we need to use DSE because at that time of executing jump instruction, its target is an expression of symbolic values that need to be dynamically determined by using a satisfiable instance of the current path constrain. For instance, if there is a jump instruction b lr at  $n_2$ , a satisfiable instance of the path condition  $\varphi_2$  will be used to get the concrete value of lr, then builds the CFG based on this determined target.

#### 3.3.2 On-the-fly CFG Generation

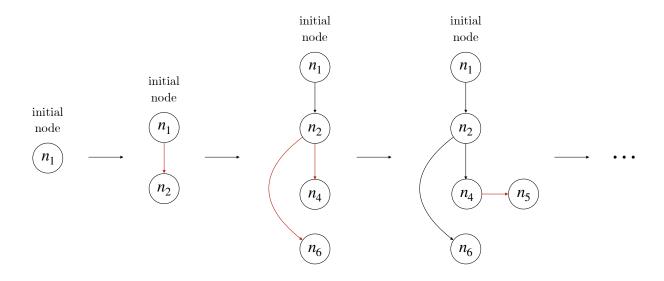

Figure 3.6: Control Flow Graph Generation by on-the-fly manner

The figure above illustrates how Control Flow Graph is generated by the on-the-fly manner. When an conditional instruction is reached, concolic testing will be applied to decide the feasible paths (red color in the figure). At each execution step, the state of a binary program is updated, including the environment of binary emulator (flags, registers, stack, and memory). This procedure is interrupted at the end of program or when reaching an unsupported instruction.

#### 3.3.3 BE-PUM for x86/Windows

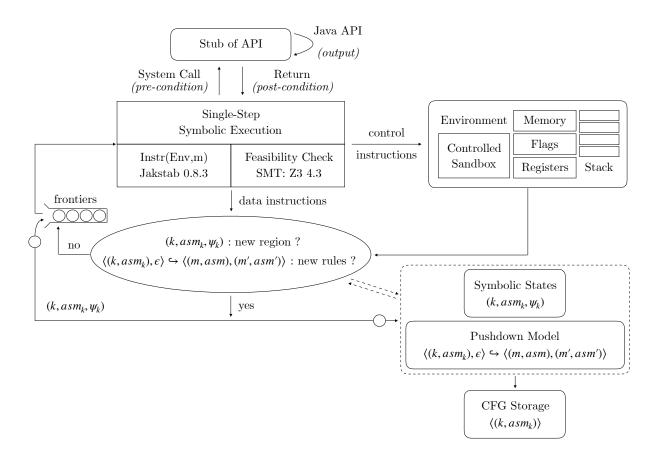

BE-PUM (Binary Emulation for PUshdown Model) [9] is a binary code analyzer concentrating on malware on Intel x86/Win32 architecture. BE-PUM inputs a binary file then applies the Dynamic Symbolic Execution technique (DSE) to generate the Control Flow Graph (CFG) of binary files in on-the-fly manner. For analyzing binary files, BE-PUM uses *JackStab 0.8.3* [22] as the disassembler, and *Z3 4.3* [23] as the theorem prover to perform test instances in the DSE process.

The figure<sup>1</sup> below shows the architecture of BE-PUM, which consists of three main elements: a CFG storage, a binary emulator, and a symbolic execution.

<sup>&</sup>lt;sup>1</sup>These figures are redrawn from the original images in the paper [9]

Figure 3.7: BE-PUM Architecture

Figure 3.8: Binary emulator in BE-PUM

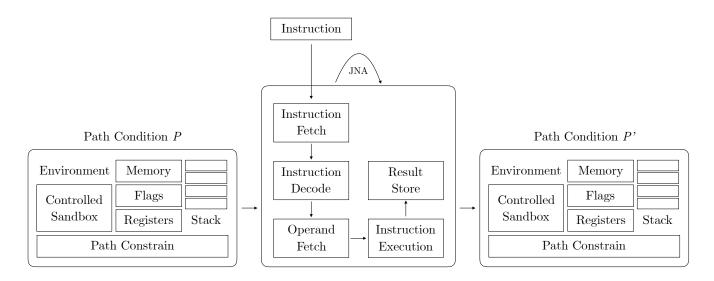

The binary emulator in BE-PUM executes the instructions. If an instruction is a branch

operation, the binary emulator updates the path constraints and the environment in the *pre-condition* P to the *post-condition* P'. Otherwise, the binary emulator only updates the environment. In BE-PUM, path constraints keep a boolean expression of symbolic values, and the environment holds the states of Memory, Stack, Registers, and Flags.

# Chapter 4

# **ARM Formal Semantics**

# 4.1 ARM Processor

ARM (shortened of Acorn RISC Machines) is a computer processors family of RISC architecture. This section briefly introduces the main components of ARM, including Stack, Memory, Register, and Flags.

### 4.1.1 Architecture

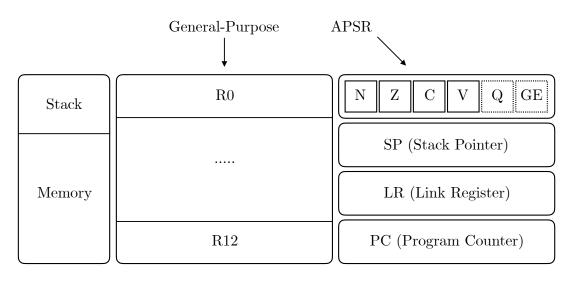

Figure 4.1: Components of ARM Architecture

This figure illustrates the main components in ARM architecture:

- 1. **Memory:** This is a physical device for temporarily stores information used during the computer operations.

- 2. **Stack:** Stack is a part of memory, stores temporary variables generated by the execution process.

- 3. **Register:** This is a place in the processor to hold data. There are five different types of registers in ARM Processors:

- General-purpose registers: It contains 13 registers marked from R0 to R12.

- *Stack Pointer (SP):* This is a register which points to the last value was stored in the stack.

- *Link Register (LR):* The LR register keeps the address returned from a function call.

- *Program Counter (PC):* (or instruction pointer) The PC register keeps the address of next instruction that needs to be executed.

- Application Program Status Register: One APSR register. It keeps conditional flags (N, Z, C, V). In some specific versions of ARM, it also holds GE and Q flags.

- 4. Flags: Flags are binary values to store states in the executed operations. The value stored in flags is either *True* (T) or *False* (F). An instruction may need to check the boolean value of flags before execution and after executing, it may also update some specific flags. In ARM, flags are stored in the APSR register.

- Negative flag (N): This flag is set by an operation if the result is negative.

- Zero flag (Z): If the result of an instruction is zero, it is set by *true*, otherwise *false*.

- Carry flag (C): When an unsigned operation's result overflows the capacity of 32-bit register, this flag is set.

- Signed Overflow flag (V): The flag works the same as the C flag, but for signed operations.

- Q: This is one of the program status flags in the APSR. It is used to indicates overflows or saturation of instruction result in only the E variants ARM-v5 or later.

- GE: The GE flags only exist in ARM-v6 and later. It can be set during the execution of parallel operations.

### 4.1.2 Cortex Series

The most popular architecture of ARM family is Cortex. It includes different series for various purpose. In general, it can be categorized into three main series: Cortex-A, Cortex-M, and Cortex-R.

Figure 4.2: Popular Cortex series of ARM

### Cortex-A

The ARM Cortex-A is the highest performance processor in ARM family. It is optimized for rich operating systems such as Android or Linux. It plays a role as the heart in the powerful technology products like smart-phones, tablet, laptop devices. The Cortex-A series can be categoried by three families: highest performance (A7X series), performance and efficiency (A5X), and lowest power (A3X).

### Cortex-M

The ARM Cortex-M is the lowest power processors, which is optimized for real-time embedded processing and micro-controller uses. As a report from ARM<sup>1</sup>, this family has already been shipped in tens of billions of device. The Cortex-M series can be categoried by three families: lowest power (M0, M0+, M23), performance efficiency (M3, M4, M33, M35P), and highest performance (M7).

### Cortex-R

The ARM Cortex-R is the family of ARM architecture that is optimized for real-time applications. Not only offers high performance, it also satisfies the requirements of real-time applications such as solid-state drive controllers.

### 4.1.3 Instructions

Each Cortex series has a different number of instructions. Even some shared instructions are used in many series, there are still some differences between other architectures. For example, the instruction SSAX in the Cortex-M4 has the same operation as SSAX in Cortex-M7, but the flags update of SSAX in Cortex-M4 is *"This instruction does not affect the condition code flags"* and the flags update of SSAX in Cortex-M7 is *"This instruction set the APSR.GE bits according to the results"*. Because we do not know exactly when they are different, we still need to process all instructions. In 5.2, an effective strategy is introduced to decide which one should be implemented.

$<sup>^{1}</sup> https://arm.com/products/processors/cortex-m$

| Variation  | Number of instructions |

|------------|------------------------|

| Cortex-M0  | 63                     |

| Cortex-M0+ | 63                     |

| Cortex-M3  | 129                    |

| Cortex-M4  | 244                    |

| Cortex-M7  | 261                    |

| Cortex-M33 | 297                    |

| Total      | 1039                   |

Table 4.1: Number of collected instructions over six architecture

The table above shows the number of instructions for each Cortex-M variation that we have successfully collected from ARM Developer Website. Each ARM instruction consists of: <code>\$name\$suffix{\$cond} \$params</code> where:

- \$name: Instruction name.

- \$suffix: Conditional suffix (optional). This is the precondition that need to be checked before execution. There is 15 different values of suffix, as described in 4.2.

- \$cond: Flags update condition (optional). In general, if the \$cond appears, this instruction updates the APSR flags based on the result of the operation.

- \$params: Instruction's parameters. It can contains some conditional params separated by |. For instance, in the instruction ADD{S} {Rd,} Rn, <Rm|#imm>, the third parameter can either be a value stored in the register Rm or a specific value #imm.

Example 4.1.1. An Cortex-M7 instruction: UMAALNE RdLo, RdHi, Rn, Rm

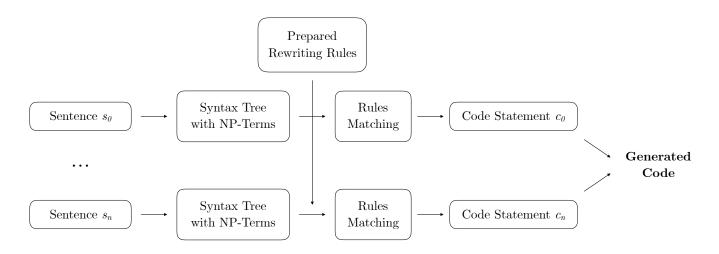

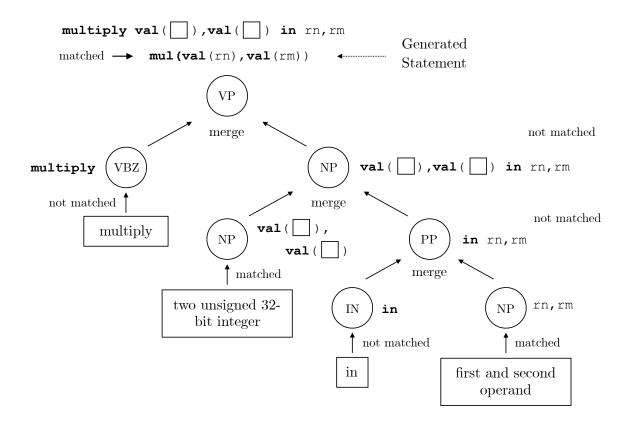

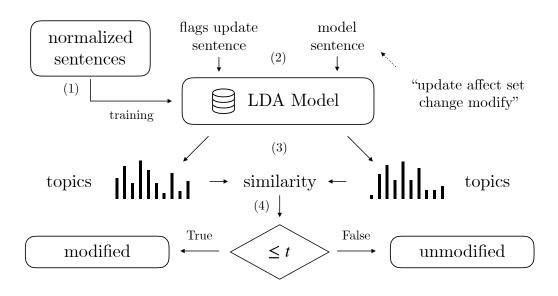

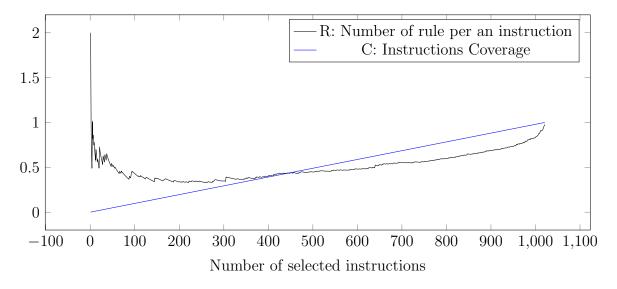

In this example, the instruction name is UMAAL. The parameters are RdLo, RdHi, Rn, and Rm. The flags update condition is omitted. It means the flags will not be modified after execution. The conditional suffix is NE means that, this instruction needs to check this condition before execution. The table below shows all possible conditional suffix in ARM and its meaning.