(�P)

�������}�O�l�g�����X�p�b�^��p����(100)Si���ւ�YSZ�����̃G�s�^�L�V��������

|

(a) �w�i 1947�N�̃N���X�}�X�C�u�̑O���A�A�����J�̃x���������ɂ����ăV���b�N���[�A�u���b�e���A�o�[�f�B�[���̂R�l�ɂ��_�ڐG�^�g�����W�X�^�̎������s���A�ő̂ł̐M���������m�F����܂����B���ꂪ�A�u�����̃f�o�C�X�v�̒a���ł��B�ȗ��A�����̎Y�Ƃ͔���I�Ȕ��W�𐋂��A�p�\�R����g�ѓd�b�A�Ɠd���i�̃t�@�W�[�@�\�ȂǁA���݂̐l�Ԑ����̂����錄�Ԃɓ��荞�݁A��X�̐����������K�Ȃ��̂ɂ��Ă���Ă��܂��B�����̔��W��LSI(Large Scale Integrated circuit)�AULSI(Ultra Large Scale Integrated circuit)�ȂǂƌĂ��A���W�σf�o�C�X�̐i���̗��j�ƌ������Ƃ��ł��A���̂��Ƃ͂Q�P���I�Ɍ������ēW�J����}���`���f�B�A�Y�Ƃ̌��ƂȂ��Ă��܂��B���Ƀ������[�f�o�C�X�ɂ����ẮA�s�������������[�̗��z�`�Ɩڂ���Ă��鋭�U�d�̃������[�̎��p���Ɍ����āA�����̌����ҒB������w�͂��d�˂Ă��܂��B |

|||||||||||

|

�}�P ZrO�Q,Y�QO�R,�y��YSZ�̌����\���} |

(b) �ړI �Q�[�g�≏���ɔ�U�d�����o���N�Ŗ�30���̍��U�d�̂ł���C�b�g���A���艻�W���R�j�A�iYSZ�j��p���āA�܂�MIS�iMetal-Insulator-Semiconductor�j�\�����쐻���A�쐻���A�y�т��̑O��̃v���Z�X�����P���邱�ƂŁA����甖���̌������Ɠd�C�I�����̌����ڎw���܂��B���ꎩ�́A�����̈�r�����ǂ�MIS-FET�̃Q�[�g�≏���ł���SiO�Q�ɑ�����̂Ƃ��ėL�]�ł���A�����I�ɂ́AMFMIS-FET(Metal-Ferroelectric-Metal-Insulator-Semiconductor Field Effect Transistor)�̃Q�[�g�≏���ւ̉��p������ɓ���Ă��܂��B |

||||||||||

|

(c) �]���̑͐ϖ@ �������X�p�b�^�@�͎Y�ƂɓK���������@�ł����A�����K�X�̎_�f�ɂ��ASi�\�ʂ��_�����Ă��܂����߁ASi���ւ̎_�����̃G�s�^�L�V���������͍���Ƃ���ė��܂����B�����ŁAYSZ�����w���`�����邱�ƂŁASi���ɃG�s�^�L�V����YSZ�����̐������\�Ƃ������̂��A�}�Q�̃v���Z�X�T�ł��B |

|||||||||||

|

�}�Q �v���Z�X�T�iYSZ�����w�`���ɂ��G�s�^�L�V����YSZ�����͐ρj |

|||||||||||

|

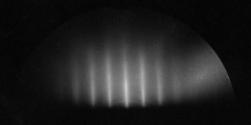

�}3 �G�s�^�L�V����YSZ������ RHEED�}�iSi<110>���˂̏ꍇ�j |

�}3��RHEED(���ˍ����d�q�����)�ʐ^����AYSZ�������G�s�^�L�V�����������Ă���l�q���f���܂��B |

||||||||||

|

�}4 YSZ/SiO2/Si�̒f��TEM�� |

�}4�̓v���Z�X�P�ő͐ς��s���������̉��f��TEM(���ߓd�q������)���ł��B RHEED�}�ɂ��YSZ�w�̃G�s�^�L�V���������͊m�F����܂������A�}4����A2.5nm����SiO�Q�w�̑��݂����炩�ɂȂ�܂����B Si��YSZ�̊E�ʂɌ`�������SiO�Q�w�͔�U�d����4�ȉ��Ə��������߁A���S�̂̔�U�d���������Ă��܂��D�܂�������܂���B���݂�YSZ�w��Si�w�̂�����ɂ�������ׂ��ȖԖڍ\���͌����i�q���ł��B �Q�[�g�≏���ɔ�U�d���̔�r�I�傫��YSZ��p���ASiO�Q�w���ɗ͂Ȃ������ƂŗǍD�ȓ�������߂�FET�̍쐻���]�߂܂��B�܂��AYSZ�����̌������̌���́A�ϑw�\���ɂ����錋�����̓`�B�Ƃ������Ӗ��ŁA������d�v�ȃt�@�N�^�[�̈�ł���ƌ������Ƃ��ł��܂��B |

||||||||||

|

�}5 �v���Z�X�̉��P�U�i�������[�h�͐ςɂ��SiO�Q�w�̐���j

�}6�@�v���Z�X���P��̃��[�N�d�����x�̖����ˑ��� |

(d)

�V���ȑ͐ϖ@ �����ŁA�͐σv���Z�X�̉��P��d��܂����B�ߎ_�����f���{�C���ƒʓd���M�ɂ��Si���ɂ��悻�Qnm�̎_�������`�����A���̌�������b�`�ő͐σ��[�g�̑傫��YSZ�̋������[�h�͐ς��{���܂��BYSZ������SiO�Q�����w���Ҍ����Ȃ���A���nSi�̌��������E���A�G�s�^�L�V�����������čs���܂��B���̂���SiO�Q�w�̑w���͌������A���S�̂̔�U�d���͌��サ�܂��B�܂��A�}6�Ɏ������Ƃ���A�]���Q�[�g�≏���Ƃ��ėp�����ė���SiO�Q�ɔ�ׂē���SiO�Q���Z�����Ŕ�r����ƁA��X�̃G�s�^�L�V����YSZ������3�`4���قǃ��[�N�d���������ǂ����Ƃ��킩��܂��B�܂����݂̏��AYSZ�����̌�����10nm��SiO�Q���Z��������1.8nm�Ă���A����Tnm�ȉ��Ƃ��邱�ƂŊ��Z�������A1nm��邱�Ƃ��\�ƍl���Ă��܂��B�����AMFMIS-FET�ɂƂ��ẮA�܂������l�ƌ����܂��̂ō���̃v���Z�X�̉��P���K�v�ƍl���Ă��܂��B |

||||||||||

|

(e)

����̉ۑ� 1. �X�Ȃ郊�[�N�d���̒ጸ 2. �≏�j��ϐ��̌��� 3. C-V�����Ō�����q�X�e���V�X�̊J���̒ጸ |

|

||||||||||

|

�@�@�@�@�@�@�߂��Ă��܂��B�@�@�@�@�@ |

|||||||||||

�@�@�@�@�@�@