1. Cat-CVD法の特徴

世の中に出回っているおよそ全ての工業製品は、その表面に薄い膜(薄膜)を伴っております。それは、ペンキ塗装であったり、メッキであったり、金沢の金箔細工のように貼り付けたものであったり様々です。電子製品もまったく同じように、表面を薄膜で被覆することが行われています。電子製品の場合には、むしろ、その薄膜の特性が製品の性能を決めてしまう場合も少なくありません。例えば、液晶ディスプレイは、半導体薄膜によって画面を構成する小さな画素の濃淡、色合が制御されています。コンピューターの心臓部である半導体集積回路も、何層にも積み重ねられた多種類の薄膜がその性能を決めています。太陽電池も、その薄膜がエネルギー変換効率を大きく左右します。

このような、電子製品の性能を決める薄膜は、300℃程度以下の低温で作製しなければならないことが多く、また、その要求される特性も、今までのメッキや塗装では得られない高度なものです。(高性能な薄膜を塗布で簡単に作製できるようにするというのも、今、世界的に大きな研究テーマになっています。)今までは、この要求を、原料ガスを真空に引かれた膜堆積用チェンバーに導入し、チェンバー内に放電によりプラズマを発生させ(今は姿を消しましたが、かつての「ネオン管」は、この放電プラズマでネオンガスを叩いて発光させていました。)、そのプラズマ中の電子との衝突により分解し、その分解した種を基板に輸送、その表面に積みあがらせて膜にする、という手法で応えていました。プラズマを用いるので、この方法を「プラズマ支援化学気相堆積(Plasma

Enhanced Chemical Vapor Deposition- PECVD)法」と呼んでいます。この方法は電子産業で最も成功した薄膜堆積法の一つになりましたが、時代が進み、要求される仕様が厳しくなってくると、そのプラズマ中の荷電粒子が、基板表面や堆積中の膜表面に衝突し、欠陥を生成することが問題視され始めました。そこで、低温で高品質膜を作ることができ、かつ、プラズマによる損傷の無い薄膜堆積法が求められるようになってきたのです。

私どもの研究室で開発した、「触媒化学気相堆積(Catalytic Chemical Vapor Deposition=Cat-CVD)法」は、まさにこの厳しくなった新しい要求を満たすものです。原料ガスを真空に引かれた堆積チェンバーに導入することまではPECVD法と同じですが、Cat-CVD法では、原料ガス分子を加熱した触媒体に接触させ、そこでの接触分解反応(Catalytic

Cracking Reaction)(→「Cat-CVD」のネーミングはここから生まれています。)を用いて分解、その分解種を基板に輸送して膜にします。そのため、放電プラズマは一切用いません。この方法では、加熱した触媒体として通電加熱された金属線を用いることが多いので、Hot-Wire

CVD法、あるいは、HWCVD法とも呼ばれています。

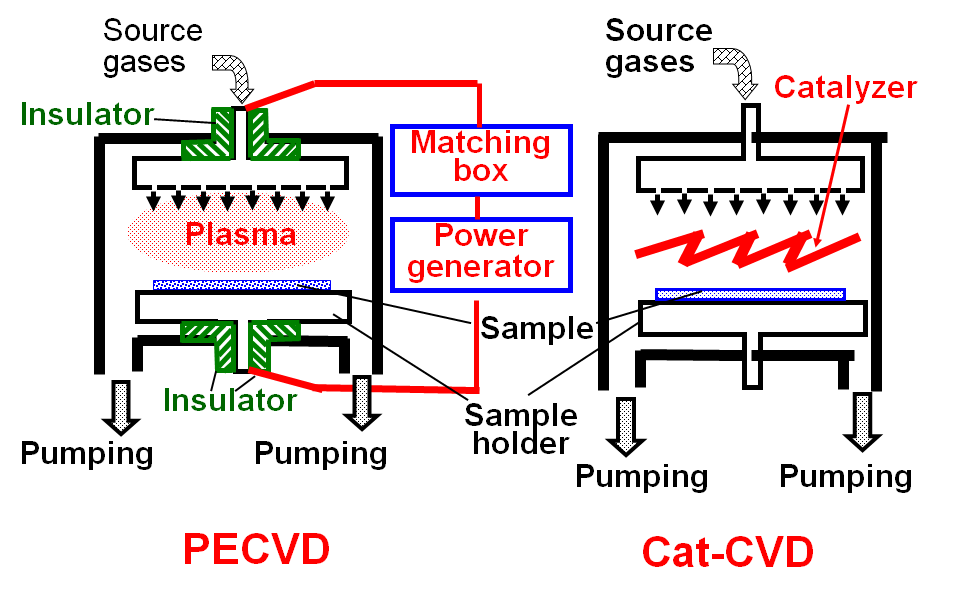

(図1)PECVD装置とCat-CVD装置の概念図。

上図(図1)に、PECVD法とCat-CVD法の装置の概略図を比較して示します。PECVD法では、電極はチェンバーから電気的に絶縁され、多くの場合、13.56MHzの高周波により放電を立て易くするのですが、そのための高周波電源、高周波電力を効率よくチェンバー内に導入するための放電調整器を必要とします。

最近、PECVD法で作られる膜が、放電周波数を上げて超高周波にし、いわゆるVery High Frequency(VHF)帯を用いると特性の向上が図れるとの報告もあり、VHF

PECVD法の研究も盛んですが、放電周波数を上げれば上げるほど、この放電調整は難しくなります。例えば、膜堆積が進むと、電極などに付いた膜が放電条件を狂わせるので、頻繁なチェンバークリーニングが必要になるなど、放電調整の難しさは量産時の大きな障害になります。

一方、このCat-CVD法には、その製膜原理から、PECVD法と較べて以下のような長所が生まれます。

① プラズマを用いないため、荷電粒子による基板および膜自体への損傷が原理的にない。

② 放電のための電気的制約がないため、基板ホルダーに量産に必要な機械的仕掛けを組み込み易くなる。

③ 立体形状の試料に対しても、先端放電などを心配することなく膜堆積ができるため、例えば、剃刀の先端や様々な形状の機械部品などに均質な

コーティングが可能になる。

④ 装置構成が簡単なので、装置コストを下げることができる。

⑤ 触媒体の設置面積の拡大により、大面積堆積が可能になる。

⑥ 垂直に垂らした触媒体の両側に基板を縦に設置することで、一度に2倍の量の膜堆積ができ、製膜の生産性が向上する。

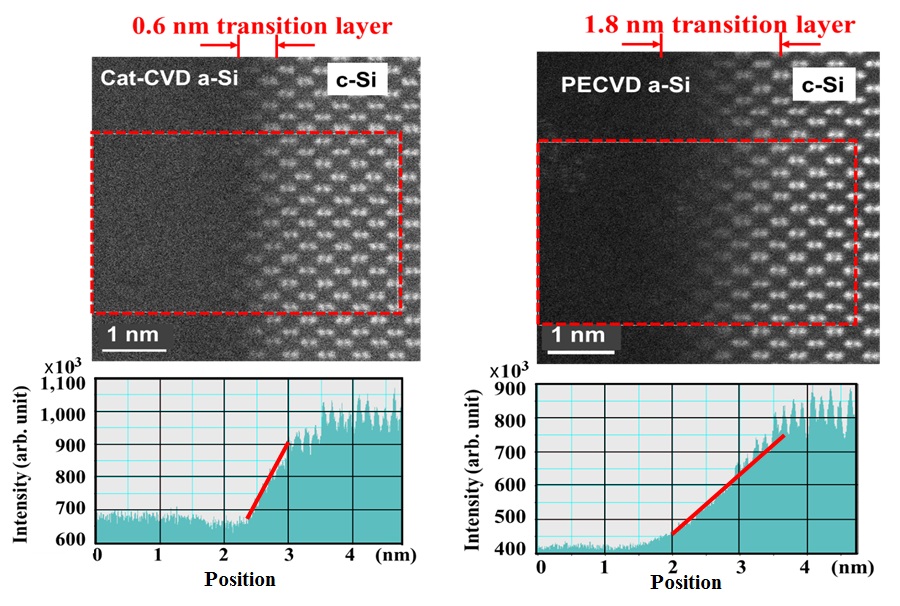

(図2)Cat-CVD法で作製したa-Si(アモルファス・シリコン)/c-Si(結晶シリコン)の界面(左)と、PECVD法で作製した同様な界面(右)のSTEM像と結晶シリコンの信号強度の位置依存性。

(図2)は、①で述べた基板への損傷が具体的にどのようなものかを示した、空間分解能0.08nmの、JAISTが誇る世界最高レベルの超高分解能走査透過型電子顕微鏡(STEM)を用いた観察像を示しています。(このクラスの空間分解能を得るには、室や床の機械的振動を抑えることは勿論ですが、音による空気振動を抑える工夫も必要になります。)結晶シリコン(c-Si)基板の上にCat-CVD法を用いてアモルファス・シリコン(a-Si)(結晶性がなく原子がランダムに配置されているシリコン(Si)の固体。)を堆積した場合と、PECVD法を用いて、a-Si膜を堆積した場合の、界面での原子像を比較しています。この試料では(110)方向から観察していますが、この空間分解能ですと、Si-Siのペアーが見られるなど、c-Siの原子配列を綺麗に見ることができます。

Cat-CVD a-Si/c-Si界面では、そのSi-Siのペアーが2つ程度見えたところで、a-Si層になりますが、PECVD a-Si/c-Si界面では、それが4、5個見えながらゆっくり画像が薄れてa-Si層になっています。図の下にSi原子の信号強度の位置依存性も併せて示しています。結晶性があると、Si原子からの信号は強度を強められて大きくなりますが、結晶性の無いアモルファス相では、信号強度は小さくなります。すなわち、この下の図は、c-Siからa-Siに移る界面の遷移層幅を示しています。この図が示すように、Cat-CVD

a-Si/c-Si界面の遷移層幅は0.6nm以下ですが、PECVD a-Si/c-Si界面でのそれは1.8nm以上にもなります。この観察はPECVD

a-Si膜をJAISTだけでなく、複数の関連企業のご協力で作って頂いたりして複数回行っていますが、遷移層幅の値はいつも同じような結果となり、再現性があります。

STEMによる観察では、厚さ15nm程度の試料を電子ビームが透過して観察していますので、界面遷移層幅の大小は、そのまま界面の凹凸の大小を示していることになります。PECVD法では、加速された荷電粒子が獲得するエネルギーは、プラズマ端に生まれるシース電圧程度で、そのシース電圧は、ガス分子と放電周波数にも拠りますが、13.56NHzの通常の周波数を用いたPECVD法では、概ね数10V程度になります。c-Si中の1個のSi原子を弾き跳ばすのに必要なエネルギーは15-20eVと言われていますので、それよりは大きなエネルギーを持った多数の荷電粒子がc-Si表面を叩くのですから、PECVD法を用いた場合に、a-Si/c-Si界面に1.8nm以上の凹凸が生じることは不思議なことではありません。今までは、この程度の界面の凹凸を許容して電子製品を作っていたのですが、やがて、一層高いレベルの界面が求められる時には、もはやPECVD法では対応できなくなると思われます。

また、⑤で述べた、堆積面積を容易に拡大できるところも、Cat-CVD法の大きなメリットです。通常のPECVD法では、堆積面積が大きくなると、高周波の定在波が立ち、膜均一性が失われます。13.56MHzの周波数の電波の波長は真空中で約22m、中にガスなどが入りますと電波の伝播速度が遅くなりますので、波長はもっと短くなります。この時、波のピーク値と振幅が0となる節の距離は1/4波長のため、約5m程度になり、例えば、基板サイズが2mもある大型装置では、この定在波の影響による膜堆積の不均一さは無視できなくなります。そのため、膜質を向上させようとして、放電周波数を、例えば60MHz位に上げようものならば、1/4波長の長さは、真空中ですら2.5m程度になってしまい、単純な方式では、大型基板の膜均一性は取れなくなります。

ただし、PECVD法でも、13.56MHzの放電周波数に対して、大面積で均一堆積を実現する方法も開発されています。ホローカソード方式という放電形式の採用です。大きな電極版の1部に、直径が10mm未満、深さがやはり10mm位の円筒形のホールを開けます。この円筒形の底の部分にはガス噴出し口と、周辺とは電気的に絶縁された放電電極が仕掛けられています。すなわち、大きな電極板の中の、直径10mmに満たないホールの中を、あたかも一つのチェンバーの様にして、そこで放電をさせてガスを分解するのです。そのホールの中の放電形式をホローカソード放電と呼びます。そのようなホローカソードを、数cmから10cm程度ごとに格子状に並べれば、その電極板のサイズ分だけ大きな基板にも膜堆積できるのです。実際、液晶ディスプレイ用の薄膜トランジスタを製造するPECVD装置は、このような方式で、基板サイズが3mに迫る、「第10世代」と呼ばれるものも作られています。ここでは、その多数配置された、各ホローカソードに同じ強度の放電をさせなければならないという難しい問題はありますが、今はそれらを克服し、立派に量産機として活躍しています。ただし、高周波放電は、周辺に膜が付くと放電条件が変わって調整のし直しをする必要があるため、付いた膜を頻繁にエッチングして除去する工程も必要になります。今は、これを、その大きな電極板の外から、大出力のマイクロ波を各ホローカソードに供給、三フッ化窒素(NF3)などのエッチングガスも併せて導入することで対処しています。NF3は価格の高いガスですし、ハロゲン系のガスの使用は真空系にそれなりの材質と設備が要求されますので、このシステムは決して安価ではありません。

Cat-CVD法では、このような複雑な機構を一切用いず、ただ単に、触媒体線の張る面積に応じて堆積面積を拡大できますので、そのメリットの大きさをご理解頂けると思います。

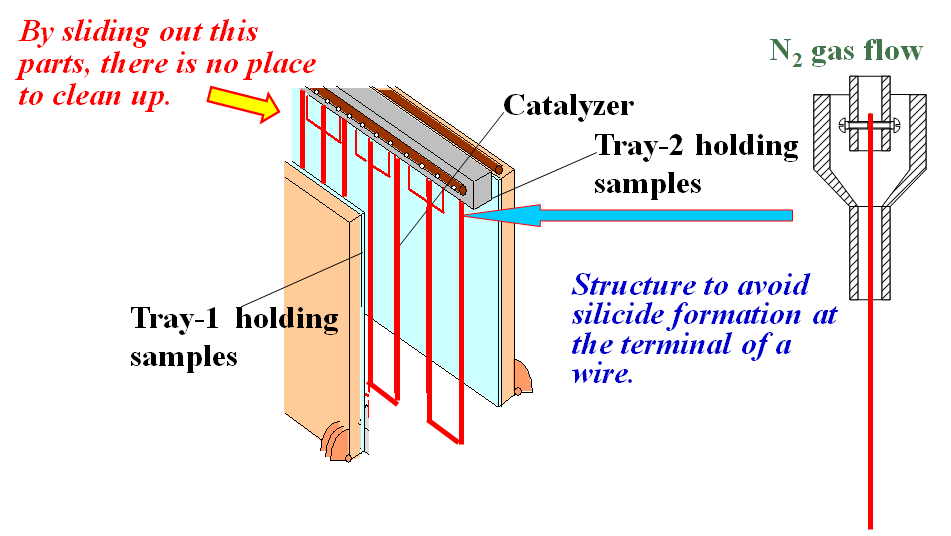

(図3)縦型Cat-CVD装置の概要。触媒体線を縦に吊るし、その触媒体線の両側に一度に膜堆積を行う。

ところで、上図(図3)は、⑥で述べた、垂直に垂らした触媒体線の両側に基板を設置した場合の装置の概念図です。触媒体を上から吊るし、その固定部分、基板トレイの上部の搬送部分、全てを定期的に交換して洗浄すれば、それ以外の部分は、堆積ごとに交換される基板トレイに隠れていますので、堆積チェンバー自体のクリーニングを省くことができる大きなメリットが生まれ、膜堆積量の増大とともに、生産性の向上に寄与します。

プラズマによる原料ガスの分解反応を用いないCat-CVD法には、もう一つの長所が生まれます。それは、

⑦ Cat-CVD法における原料ガスの利用効率は、PECVD法の5倍から10倍も高くなる。

というものです。

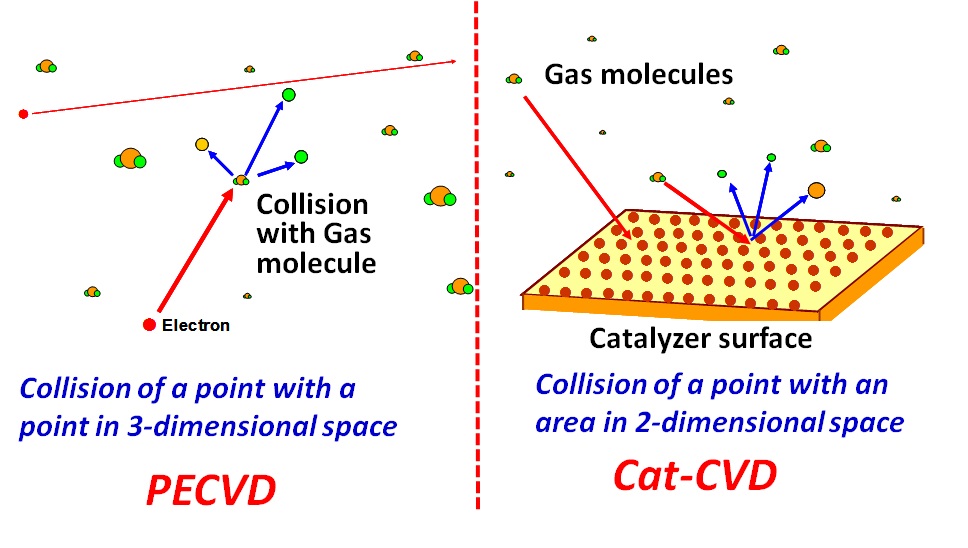

PECVD法では、原料ガス分子は、プラズマ中で加速された電子との衝突で物理的に分解されます。すなわちPECVD法では、下図(図4)の左に模式的に示すように、減圧チェンバー内で、小さな分子と小さな電子の衝突、すなわち3次元空間内での「点」と「点」の衝突を利用します。そのため、PECVD法における原料ガス分子の分解反応はそう頻繁に起こるものではなく、中には、全く分解されず、膜堆積に寄与せずに無駄に排気されてしまう分子もあります。PECVD法におけるガス利用効率はそう高いものではありません。

(図4)PECVDとCat-CVDにおける、ガス分子分解機構の模式図。

一方、Cat-CVD法では、(図4)右図に示すように、原料ガス分子は、触媒体、すなわち固体表面と反応します。言わば、「点」と2次元の「面」との衝突を利用します。ですから、ガス分子の分解確率はPECVD法に較べて飛躍的に向上し、条件にもよりますが、ほぼ100%の原料ガス分子が分解されます。実際、装置メーカーの測定によると、Si系薄膜の原料ガスであるシラン(SiH4)ガスをCat-CVD装置に導入してa-Si膜を堆積すると、排気ガスに含まれる残留SiH4ガスは2%以下であったとのことです。SiH4ガスは、半導体産業になくてはならないガスですが、爆発性のあるガスで、その取り扱いが法律で厳しく管理されている特殊なガスです。そして、その排気の無害化も大きな問題です。Cat-CVD法では原料ガスの利用効率が高く、その危険ガスの使用量が少なくて済むため、工場における危険ガスの保管量を1/10近くに減らすことができ、かつ、排気の無害化設備も大幅に縮小できます。Cat-CVD法を大面積基板の大量生産に使用するメリットは絶大です。

2. Cat-CVD法における触媒体表面の反応

それでは、Cat-CVD法におけるガス分子分解の鍵となる触媒体表面で、何が起きているのかを見てみましょう。原料ガス分子と触媒体材料によって起きる現象は様々ですが、ここではまず、a-Si膜の堆積を考え、タングステン(W)線を触媒とし、SiH4ガスを分解する場合を考えてみます。

ガス分子が固体表面に飛来した場合、2つのルートの反応が起きます。一つは、一瞬、物理吸着(化学結合は形成せず、ワンデルワールス力という双極子を基本とする比較的弱い電気的力で固体表面とつながるだけの吸着)をしたとしても、そのままその固体を離れ、ガス分子は何ごとも無かったかのように振舞うものです。

もう一つは、ガス分子が固体表面で解離し、バラバラになって化学結合をするルートです。ガス分子がある距離以内に接近すると、固体表面の結合手の誘惑が強く、ガス分子は分解してでも、その固体原子と化学結合をしようとします。ガス分子が単独でいるよりも、固体原子と分解して化学結合をした方が、元々の分子を構成していた時よりも合計したエネルギーが下がる時に、この反応が起きます。

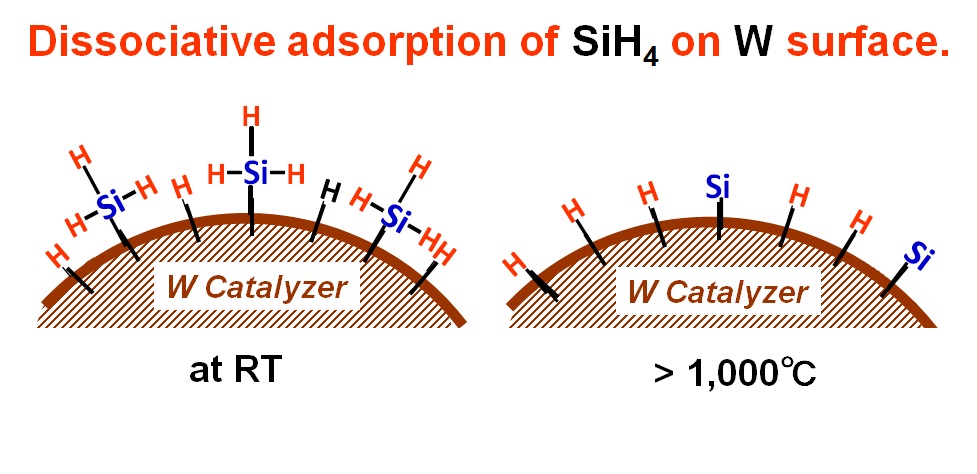

(図5)W触媒体表面でのSiH4分子、解離吸着の様子。室温と1,000℃以上の場合の比較。

(図5)左図にその概念図を示します。W表面に飛来したSiH4分子は、室温においても、SiH4→SiH3+H に解離し、W-SiH3とW-HとなってW表面に解離吸着すると言われています。すなわち、SiH4の分解自体は、熱で行われている訳ではなく、化学反応をともなうこの解離吸着

(Dissociative adsorption) によってなされているのです。

これは、Wの温度が室温の場合ですが、次にWの温度が上昇した時の場合を考えてみます。W-SiH3の結合は、Siの後ろに3個のH原子が付いているとはいえ、後で問題となるW-Siの強い結合のため、そうは簡単にW表面から脱離しません。しかし、Wの表面温度が1,000℃を超えると、Wから受け取る熱のために、W-SiH3は大きく揺すられ、HはWに接近する確率が上がり、直にWと結合して、W-Siと4×(W-H)の形になって反応が終わります。別の言い方をすれば、Wの表面温度が1,000℃以上では、W表面には、Wの結合サイトを5個使った、W-Siと4×(W-H)の形しか存在できなくなるのです。その様子を、(図5)右図に示します。このように、ある温度の触媒体上での解離吸着形は、ガス分子と触媒体材料の組み合わせで決まり、1,000℃以上のW上のSiH4の解離吸着形は、Si+4Hですが、例えば、アンモニア(NH3)の解離吸着形は、N+NH2

とW表面の2サイトのみを使ったものになることが知られています。要するに、素反応の解離吸着形(SiH4の場合はSiH3+H)から、触媒体から受け取る熱によってどの形になるまでその触媒体表面に留まっていられるのかによって、解離吸着形が決まるのです。

ところで、Wの温度が1,000℃以上でW-Siと4×(W-H)の形になる際、W-Hの結合からは、比較的容易にH原子が熱脱離するのですが、W-Siの結合は外れにくく、一部は残ってシリサイドを作ってしまいます。Siの熱脱離を増速し、このシリサイド化を防止するために、Cat-CVD法では、SiH4の分解の際に、W触媒体温度を1,800℃位にまで上げます。触媒体温度を高温にするのは、SiH4を熱分解するためではなく、シリサイド化を防止するためなのです。実際、Wの代わりに、タンタル(Ta)を触媒体として用いると、Siの熱脱離温度がWよりも低いため、触媒体温度を1,700℃程度に下げることができます。

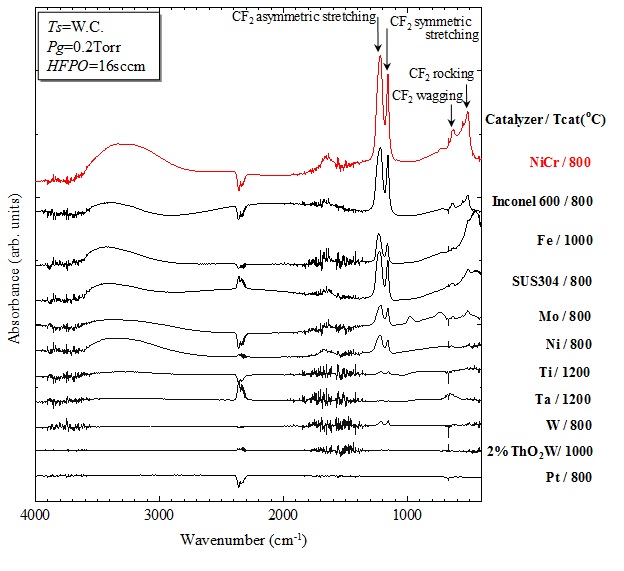

(図6)HFPOガスを用いてPTFE膜を作製する際の、触媒体材料と触媒体温度ごとの、作られた膜の赤外吸収スペクトル。ピークの大小は、単純に膜厚に対応する。

これは、SiH4を接触分解してa-Si膜を作る時の話ですが、HFPO (Hexa-Fluoro-Propylen-Oxide)と言う原料ガスを用いると、PTFE

(Poly-Tetra-Fluoro-Ethylene) (商品名「テフロン」)膜が作れます。(図6)は、作られた膜の赤外吸収スペクトルを、膜作製時に用いた触媒体線と触媒体温度ごとに示したものです。赤外吸収ピークとしては、フッ素(F)と炭素(C)の結合に関連したピークが示されています。膜形成条件は全て同じとし、触媒体温度は800-1,200

℃、ガス圧は2.7 Pa (=0.2 Torr)、堆積時間は30分としています。赤外吸収ピークの大小は、単純に堆積した膜厚に比例しており、この図で、併せて、膜堆積のし易さを表しています。

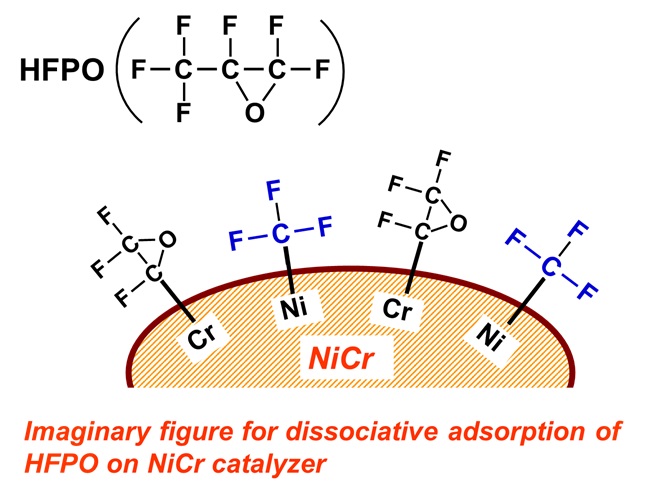

この図は、触媒体金属の種類により、膜堆積速度が大きく変わることを示しています。興味深いのは、ニクロム(NiCr)やインコネル、ステンレス(SUS)など、ニッケル(Ni)含有合金を用いると、膜堆積速度が速いのに、例えば、Ni単体になると、逆に膜堆積速度は落ちてしまうことです。そのメカニズムは完全に理解できた訳ではありませんが、例えば、

NiCrを触媒体として考えた場合、下図(図7)のような触媒体上での分解形が予想されます。すなわち、HFPO、F3C-FC-O-CF2 は、Ni-CF3

とCr-FC-O-CF2の形で解離吸着するとまず仮定します。ここで、-FC-O-CF2との結合が、Niよりも他の元素との方が形成され易ければ、Ni単体より、その -FC-O-CF2 の引き受け手の多い、Ni合金の方が、解離吸着反応は進行し易くなるはずです。(このHFPOの解離吸着形に関する説明は、全てイメージを伝えるための想像にもとづくもので、実際は、現時点では、ここに描く結合形の真偽は保証されていません。HFPO

は F3C-C(=O)-F とCF2 に分解することは広く知られていますが、そばに触媒体が存在する場合の分解形は不明です。)いずれにせよ、(図6)に示す結果は、Cat-CVDにおいて、触媒体の表面反応が如何に重要か、原料ガスの分解が単なる熱分解ではないことを、如実に表しています。

(図7)NiCr触媒体上でのHFPO分子の解離吸着形の想像図。(実験による証明などはなく、概念説明のための完全な想像図)

下の(図8)は、Cat-CVD法でPTFE膜をSUS基板の半分に堆積し、それに水をスポイトで一滴づつ垂らした時の、超撥水実現の様子の動画、(図9)は、同様にPTFE膜を木綿のハンカチ上に堆積した場合の超撥水性を示す動画です。Cat-CVD法により作られたPTFE膜の威力は大変なものです。

このPTFE膜に限らず、最近は、欧米を中心に、このCat-CVD法、あるいは、その派生技術を用いた、ポリプロピレン、アクリルなどの高品質有機薄膜合成の研究が活発化しています。

↑(図8)ステンレス基板の半分にCat-CVD法によりPTFE(商品名「テフロン」)膜を堆積し、PTFE膜を堆積した部分が、超撥水性を示すこと表した動画

画面左がPTFE膜を堆積した部分。

↓(図9)木綿のハンカチにCat-CVD法でPTFE膜を堆積した場合の超撥水性を示す動画。

上がPTFE膜を堆積したもの。下が堆積処理をしていないもの。

3. Cat-CVD膜の特長と応用例

このような原理で作られるCat-CVD膜には、従来からのPECVD膜とは異なる幾つかの特長が生まれます。堆積チェンバー内の気相中にH原子密度が高いことは説明しましたが、この高い密度のH原子は、成長中の薄膜の表面に作用し、そこにあるH原子を、H2を作ることで引き剥がします。一般的に、上にも述べましたが、半導体産業では水素化合物ガスを多用するため、それから作られる膜には、どうしてもH原子が含まれてしまい、それが膜本来の骨格原子の密度を下げたり、膜特性の温度不安定性を招いたりしています。Cat-CVD法では、そのH原子密度が下げられる、逆に言えば、膜の骨格となる本来必要な原子の密度を高められるメリットが生まれます。

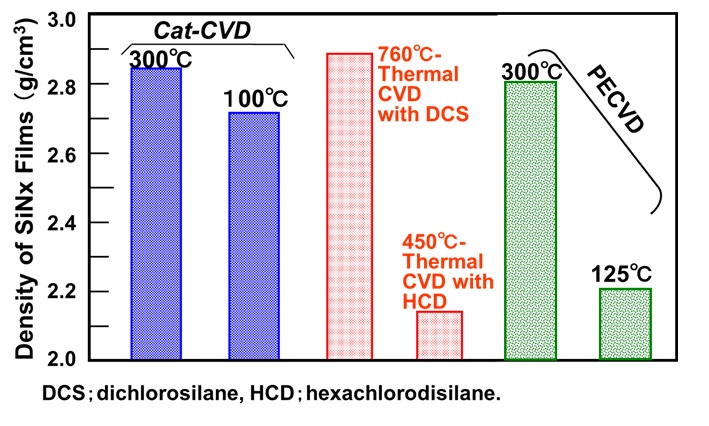

(図10)Cat-CVD法、高温熱CVD法、PECVD法で製膜されたSiNx膜の膜密度。基板温度も書かれている。

上の(図10)に、Cat-CVD法によりSiH4とNH3の混合ガスからシリコン窒化(SiNx)膜を作製した時の膜密度を、原料としてDCS (Di-Chloro-Silane) を用いて760℃の熱CVD法で作製した膜、HCD (Hexa-Chloro-Disilane) を用いて450℃の熱CVD法で作製した膜、および、125℃と300℃の基板温度でPECVD法で作製した膜のそれと比較して示します。Cat-CVD膜は、基板温度300℃と100℃の両方で製膜された場合を載せています。Cat-CVD法で作られたSiNx膜は、堆積時の基板温度が低温化しても、膜密度が高い膜であることが見出されます。膜密度が高いために、Cat-CVD SiNx膜は低温堆積時も水分などのガスバリヤ膜として働きます。そのため、Cat-CVD SiNx膜は、基板表面に損傷を与えない長所と合わせ、電子デバイスの表面保護膜、あるいは、ガスバリヤ膜としての応用が期待されています。

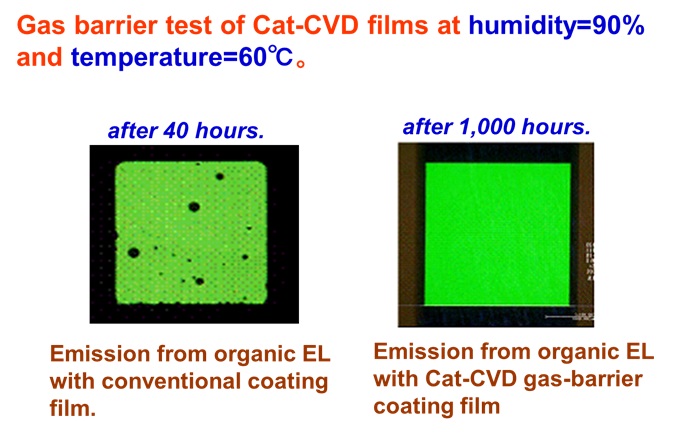

(図11)Cat-CVD SiNx膜を中心とするガスバリヤ膜で表面を覆った有機EL(右)とガスバリヤ性のない膜で表面を覆った有機EL(左)の発光時間とその発光の様子を示す写真。湿度90%、温度60℃の加速試験の結果。

(図11)は、水分により簡単に劣化してしまう有機材料を用いた発光デバイス、有機ELのガスバリヤ膜として、ガスバリヤ性の高いCat-CVD膜を堆積した場合と、ガスバリヤ性のない膜を堆積した場合に、湿度90%、温度60℃の条件下で、1,000時間、あるいは40時間曝した時の、表面の発光状態を示す写真です。Cat-CVD膜で覆われた有機ELは、1,000時間後も、いわゆるDark

spot と呼ばれる非発光点が生まれることなく、発光し続けていることが示されています。この環境下での発光は、通常環境下の約15倍加速されると言われていますので、Cat-CVD膜で保護された有機ELは少なくとも、15,000時間以上は、通常の環境下ならば発光し続けていることになります。

下表に、Cat-CVD法の応用例を、実用化の状況も併せてまとめます。Cat-CVD技術の応用には、いわゆる膜堆積以外に、Cat-CVD装置内で発生する接触分解種(多くの場合ラジカル)を利用するものもあります。Cat-CVD装置内では、効率良くH原子がH2ガス分子から生成されますので、その高密度H原子を用いた基板表面洗浄、表面エッチング、基板上のフォトレジスト除去、溶液プロセスで形成された配線ラインの有機バインダー低温除去による低抵抗金属配線の形成、など多くの応用が検討されています。また、ホスフィン(PH3)やジボラン(B2H6)ガスをCat-CVD装置内で接触分解されて生成される種を使うと、リン(P)原子やボロン(B)原子を結晶Si内に、実に、わずか80℃と言う低温で導入することもできます。この方法を、我々は「Cat-doping」と名付けて、現在、その特性と応用技術を検討中ですが、それについては、次節に述べます。

Cat-CVD技術の応用例と実用化の状況

| 応用分野 | Cat-CVD膜適用箇所 | Cat-CVDを用いた効用 | Cat-CVDを用いる理由 | 実用化の状況 |

|---|---|---|---|---|

| Si ULSI | 微細MOS gate side wall、 ライナー窒化膜など。 |

負バイアス印加MOS特性劣化(NBTI)寿命を従来法より2桁延長 | Cat-CVD SiNx膜中にはNBTIの原因とされるHが少ない。 | ALDとの競争。 実用化はまだ。 |

| 化合物半導体 デバイス |

① GaAs,GaN超高周波 トランジスタの保護膜 ② 光通信用半導体レーザー の保護膜 |

① GaAs,GaN超高周波トランジスタ の高出力化、高周波数化 ② 光通信用半導体レーザーの高出力・ 長寿命化 |

緻密で、ストレスも低く、バリヤ能力の高いSiNx膜が、下地基板へのプラズマ損傷(新欠陥生成)なく得られる。 | ①、②ともに、実用化成功 |

| ディスプレイ 分野 |

① a-Si TFT ② As deposited poly-Si TFT ③ 有機EL防湿バリヤ膜 ④ コピー機感光ドラムの 光導電膜 |

① 同じOn電流に対しTFTのOff電流を 1桁以上低下、特性の長期安定性に 優れる。 ② 移動度40 cm2/VsのTFTの低温形成。 ③ 有機ELに、60℃、湿度90%の加速 環境で1,000時間の寿命。 ④ 高速で膜堆積ができ、原料ガスの 利用効率が高い。 |

① 暗導電率低く、活性化エネルギー 高い。電流印加による欠陥生成が 少ないa-Si膜が作れる。 ② 300℃で直にpoly-Siが作れる。 ③ Cat-CVD膜は、堆積時損傷なく 低温堆積でも高いガスバリヤ性。 ④ Cat-CVD a-Si膜は高速堆積時に 高光導電率、高原料利用効率。 |

①②③検討中。 ④は商談中。 |

| 太陽電池 | ① 薄膜太陽電池のa-Si膜 ② 結晶シリコン太陽電池の 反射防止SiNx膜 ③ a-Si/結晶Siハイブリット 太陽電池 |

① PECVD a-Si太陽電池と同等の効率 を堆積速度4倍で実現。 ② 表面再結合速度の小さい太陽電池 の実現。 ③ 低温工程で効率向上が図れる。 |

① Cat-CVD a-Si膜は光劣化が少ない。 原料ガス利用効率が高い。 ② 膜堆積時の下地基板損傷が少ない。 ③ 下地基板損傷が少なく、ガス利用 効率高い。 |

一部応用が既に 実用化し、大規模量産中。 |

| 新デバイス | カーボンナノチューブ (CNT)TFTコート膜 |

CNT TFTを初めて大気中で動作 | 低無損傷・SiNx膜高ガスバリヤ性 | 基礎実験中 |

| 繊維関連分野 | 木綿などへのPTFE膜堆積 | 肌触り、通気性を損なうことなく撥水性付与。膜が繊維周りをカバレージ良く完全被覆。 | 緻密で微細形状上でのカバレージの良いPTFE膜の室温堆積が可能。 | 検討中 |

| 機械加工分野 | ① 自動車部品など過酷環境 で長時間使用する機材の 表面コート ② 鋭利な先端を持つ機材の コート |

① 従来のメッキに比べ1桁以上の安定 使用寿命の確保 ② 鋭利性を失わず、低摩擦化の 実現 |

① 緻密でガスバリヤ性、耐環境性(耐 酸性)のあるSiNx製膜可能 ② 厚み10nmで高品質なPTFE膜が形成 可能 |

① 検討中 ②高級髭剃り刃と して製品化 |

| 包装基材関連 分野 |

食品包装材および医薬品包装材のガスバリヤ膜 | 透明で直接電子レンジにかけられる食品包装材の実現 | 透明で、ガスバリヤ能力の高いSiNx/SiOxNy膜の100℃以下の低温堆積が可能。 | 実用化未定 |

| 高密度活性種の応用分野 | ① フォトレジスト除去 ② 真空紫外リソグラフィー 用反射ミラー表面洗浄 ③ インクジェット配線の 高品質化 ④ B、P原子の結晶Siへの 低温ドーピング ⑤ N原子のSiC基板への 低温ドーピング |

① 高ドーズイオン注入されたフォト レジストを残渣無く除去。 ② 反射率を劣化させずに表面に付着 した炭化汚染層除去 ③ Cuインクを用いた配線の低抵抗化 に初めて成功 ④ 80℃の低温での結晶Siへのドーピ ングによる導電率、伝導型制御に 成功 ⑤ SiC基板に350℃でN原子導入成功 |

高密度Hの発生とその発生量を触媒体温度調整で数桁制御できる。装置構造が簡単である。 | ① 装置商品化 ② 商品に組み込み 済み ③ 基礎実験の段階 ④ Cat-dopingと して短期間で 実用化可能性大 ⑤基礎実験中 |

4. Cat-CVD技術の新しい展開―「Cat-doping法」の誕生

上述の通り、PH3、B2H6ガスなどのドーピングガスをCat-CVD装置に入れて、それらガスの接触分解種を生成、それに結晶Siなどを曝すと、結晶Si中に、わずか80℃という従来全く予想もしなかった低温でP、Bがドーピングできることを発見し、この新しい不純物導入法を「Cat-doping法」と名付けました。

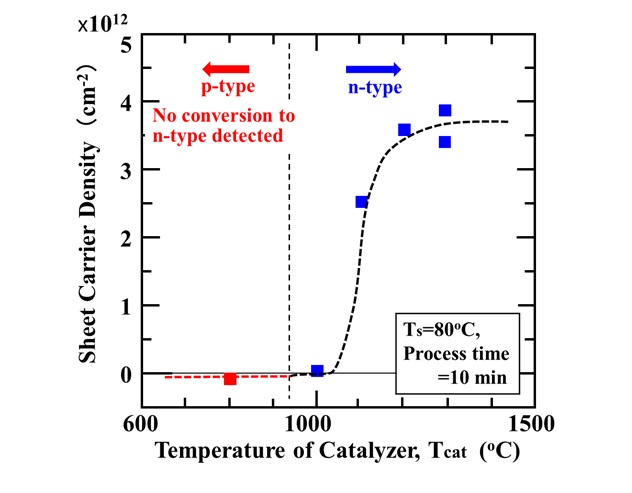

(図12)P原子を基板温度80℃でp型結晶Siにドーピングした際の、導電型とシートキャリヤ密度のW触媒体温度依存性。

(図12)は、PH3ガスを、Wを触媒体として分解、その分解種を用いてP原子をp型結晶Siにドーピングした際の、結晶Siの表面から測定したシートキャリヤ密度、伝導型を、触媒体温度の関数で示したものです。触媒体温度が800℃以下では、結晶Siは元々のp型を示していますが、触媒体温度が1,000℃以上では、導電型はn型に反転し、触媒体温度の上昇とともに、シートキャリヤ密度は上昇しています。このことは、この低温ドーピングは、触媒分解された種の存在が決定的に重要であることを示しています。

同様な低温ドーピング法としては、Plasma dopingなどが知られています。これは、通常のPECVDに近い装置で、PやBをドーピングする方法ですが、一般的には、電極にバイアス電圧をかけますので、いわゆる、マス分析の無いイオン注入ともみなされていました。もっとも、プラズマを用いると、すでに述べたように、必ず試料の置かれた電極近傍にシース電圧が発生しますので、例え、バイアス電圧0

V でも、低エネルギーイオン注入が起きていると考えれば、結晶シリコンにPやBが低温でドーピングされても不思議ではありませんでした。その意味で、Cat-doping法の発見は画期的です。Cat-doping法の発見は、もしかすると、Plasma

dopingにおいても、ある比率では、シース電圧の存在がなくても、結晶Si中に導入されていたPやB原子があったかもしれないことを想像もさせます。大切なことは、Cat-dopingでは、電位の存在を排除し、かつ、基板表面に一切のプラズマ損傷を与えない条件で、PやBが低温でドーピングできることを示したことです。

このCat-dopingは、結晶Si表面近傍の低温でのキャリヤ密度の制御を可能にしたため、例えば、太陽電池の反射防止膜として従来から用いられていたSiNx膜堆積の前に、基板の結晶Si表面に、P原子などをCat-dopingして結晶Si表面のポテンシャルを制御すると、SiNx/結晶Si

界面での電子とホールの再結合が抑制され、キャリヤの表面再結合を劇的に低下させられることも発見されています。

このCat-dopingの研究は始まったばかりですが、今までドーピングが難しかった炭化シリコン(SiC)にも、わずか350℃の低温でNドナー原子が導入できることが確認されるなど、従来の半導体不純物導入技術ができなかったことを次々に可能にしており、今後、大きく発展する可能性を秘めています。